The IIS Chip Gallery

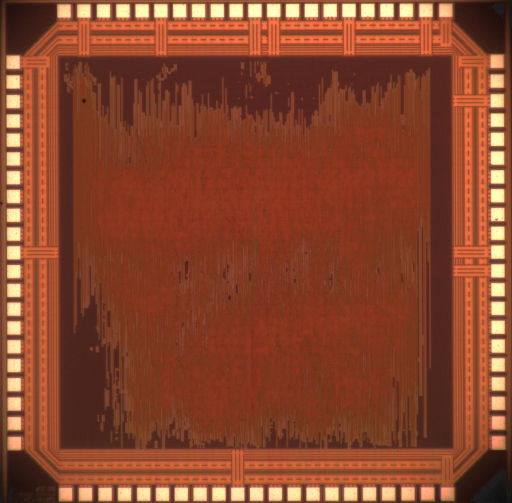

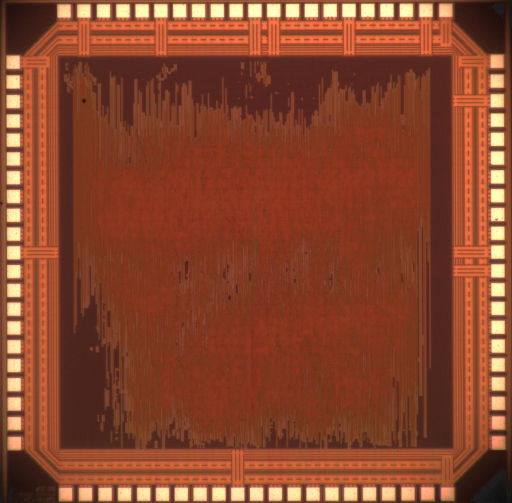

TG_Multiplier (2006)

by

| Application | Low-power |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

Various full-adder cells and 16-bit multiplier architectures have been reviewed and compared in terms of dissipated energy, propagation delay, energy-delay product and area, in view of low-power signal processing for low-frequency applications. A novel analysis instrument, the spurious activity diagram, has been set up to investigate the mechanisms of glitch activity. It was found that spurious activity is a major cause of dissipation in parallel multipliers.

Four multiplier architectures (carry-save (CSM), Wallace tree (WTM), the new transmission-gate multiplier (TGM), WTM with minimum-size transistors (WTMS)) have been integrated in a 0.18 um CMOS process. Measurements point out that, because of their shorter full-adder chains, WTM dissipate less energy than CSM and other traditional array multipliers (8.2uW/MHz versus 9.6 uW/MHz at 0.75 V). The effect of transistor sizing on power consumption is also evaluated (WTMS 6.2uW/MHz). By introducing transmission gates in the WTM, a new approach is proposed to improve the energy efficiency further (4.7 uW/ MHz), beyond recently published low-power architectures. The innovation is in combining transmission gates with level-restoring CMOS gates to suppress glitches by RC low-pass filtering, while keeping unaltered driving capabilities. The increased Vdd to Vss resistance also contributes to a significant reduction of static consumption (-66 % compared to the most leakage-efficient competitor).