The IIS Chip Gallery

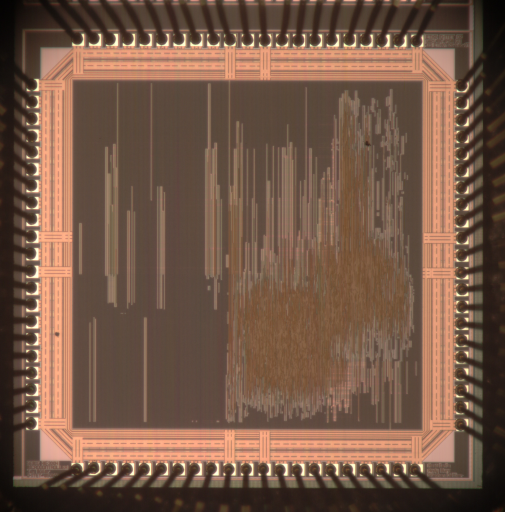

SEMIC (2007)

by

| Application | Cryptography |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 1.8 V |

| Clock | 100 MHz |

Security systems often use a small embedded 8 bit or 16 bit microprocessor. If high data rates are required, dedicated hardware, e.g. an ASIC with a cipher engine has to be added. Besides low cost, minimal energy consumption is a main issue in many applications. The challenge of this project was to find an optimum solution which meets these requirements.

The feasibility of extending an existing H8/300H 16 bit microprocessor architecture with dedicated hardware to support crypto operation has been exploited. Among other realized extensions, the mix-column operation in hardware resulted in a performance gain of a factor 2.25 for the AES algorithm. A true random number generator based on sampling the output of ring-oscillators has been implemented, too. It passed the NIST test suite. The standby mode with asynchronous wake-up capabilities, another implemented feature, reduces the supply current to 1 to 2 mA at room temperature. The GNU gdb debugging suite for the H8 processor was augmented with the new dedicated instructions. It could also be used as golden model for simulation.

The ASIC operates at 50 MHz system clock frequency with 1.3 V core supply voltage, and in excess of 100 MHz at 1.8 V.