The IIS Chip Gallery

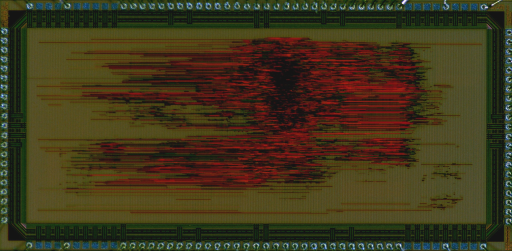

ASPE_B (2008)

Additional pictures below, click to see larger versions

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Diploma Thesis |

| Package | PGA120 |

| Dimensions | 5000μm x 2500μm |

| Gates | 400 kGE |

| Voltage | 1.8 V |

| Clock | 250 MHz |

Matrix inversion is a hard computational kernel of linear minimum mean-squared error (MMSE) multiple-input multiple-output (MIMO) receivers. The SOL processor developed at ETHZ is a reconfigurable instruction set processor (RISP) that is configurable at design-time with execution units tailored to the application to be implemented.

In this project, two matrix inversion algorithms were mapped onto the SOL-RISP, a Rank-1 update method and a divide-and-conquer method. First, the two algorithms were re-arranged to fit best onto the RISP, and the required atomic operations were identified. Next, the execution units were designed. The configuration chosen to support both matrix inversion algorithms comprised one real-valued divider (DIV), one complex-valued ALU (CALU), two complex-valued MACs (CMACs), as well as storage units (SUs), and a register file (RF) for temporary data storage. The dictionary memory (DICT MEM) stores unique instructions that are addressed by the instruction pointer memory (INSTR MEM). Finally, the backend design was performed and the assembler code implementation of both algorithms for different antenna configurations was written.

The design runs at a clock frequency of 250 MHz and occupies an area of 3.7 mm2 on a 180 nm CMOS technology. With this implementation, a 2x2, 3x3, or 4x4 matrix is inverted in 11, 59, or 83 clock cycles, respectively.