The IIS Chip Gallery

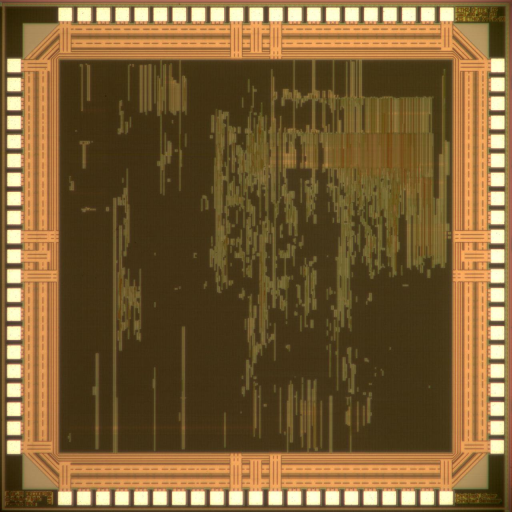

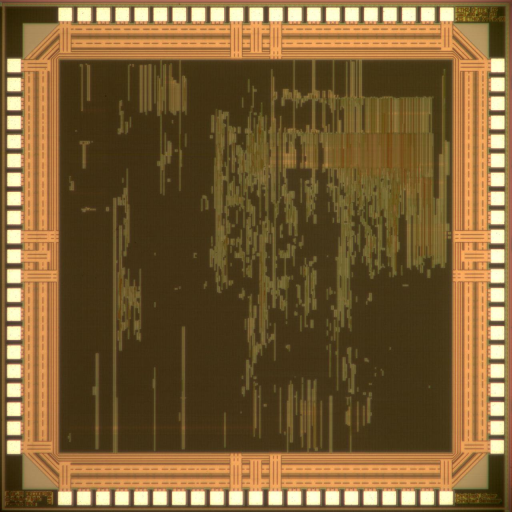

MBCJR32to4 (2008)

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 300 kGE |

| Voltage | 1.8 V |

| Clock | 250-400 MHz |

Iterative detection and decoding in multiple-input multiple-output (MIMO) wireless communication systems offers better quality-of-service and higher system throughput compared to that of soft-output MIMO detection. These gains come at the cost of significantly increased computational complexity in the MIMO detector and in the channel decoder.

The goal of this project was to evaluate the hardware-complexity and throughput of soft-input soft-output channel decoders for convolutional codes. To this end, a windowed approximation of the BCJR algorithm [Bahl, Cocke, Jelinek, and Raviv, IEEE Trans. IT, 1974] has been used (referred to as max-log M-BCJR). Five different architectures have been implemented for five different codes. These codes differ in the number of states (i.e., 4, 8, 16, 32, and 64) and achieve different error-correction capability. The 64-state BJCR decoder achieves the best error-rate performance and is compliant to the IEEE 802.11n WLAN standard.

All five M-BCJR architectures have been implemented in 180 nm (1P/6M) CMOS technology. This ASIC contains all variants except the 64-state variant,. All M-BCJR cores achieve a maximum clock frequency of 375 MHz, which leads to 375 Mbit/s. The circuit area ranges from 0.22 mm2 to 2.37 mm2 for the 4-state and 64-state decoder, respectively. See also .