The IIS Chip Gallery

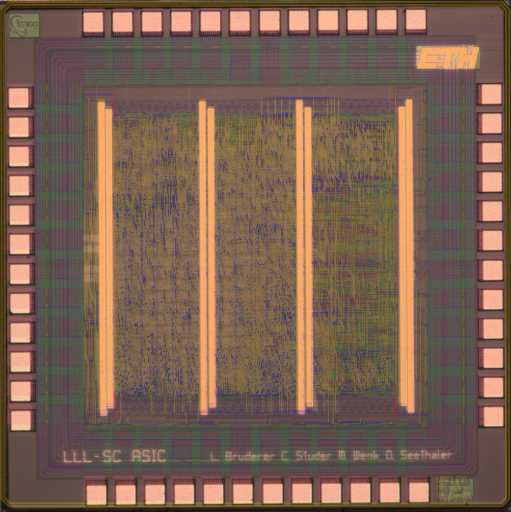

LLL (2008)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | UMC |

| Type | Diploma Thesis |

| Package | QFN48 |

| Dimensions | 1525μm x 1525μm |

| Gates | 100 kGE |

| Voltage | 1.2 V |

| Clock | 333 MHz |

This chip implements a hardware-efficient VLSI architecture of the Lenstra- Lenstra-Lovįsz (LLL) LR algorithm for SIC-based data detection.

Lattice reduction (LR) techniques were proposed to reduce the performance gap between low-complexity MIMO detection schemes and costly Maximum Likelihood detection [2] and [3]. The basic idea is to perform sub-optimum detection based on latticereduced channel matrices. This approach shifts most of the computational complexity to the preprocessing stage, which needs to be performed only when the channel state changes. Unfortunately, most communication standards require this preprocessing step to be performed under tight latency constraints, which requires high-speed LR implementations.

In this chip, a low-complexity LR algorithm for SIC-based MIMO detection that is based on the Lenstra-Lenstra-Lovįsz (LLL) algorithm and employs the Siegel criterion is implemented . In an attempt to reduce the computational complexity, the size reduction condition is relaxed and an early termination (ET) of the algorithm based on the actual execution time is employed. To reduce the performance loss in the presence of ET, the processing order of the elements in the LR algorithm has been reversed.