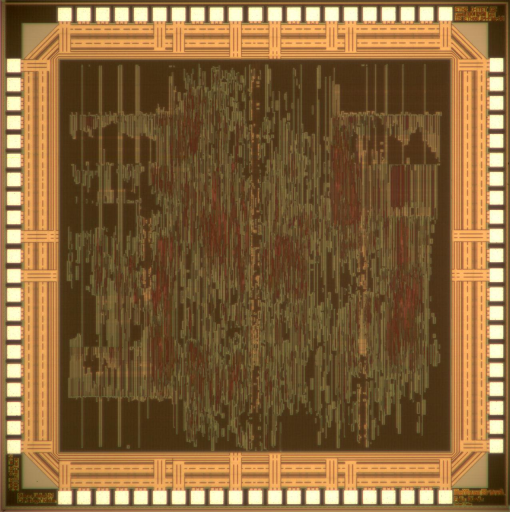

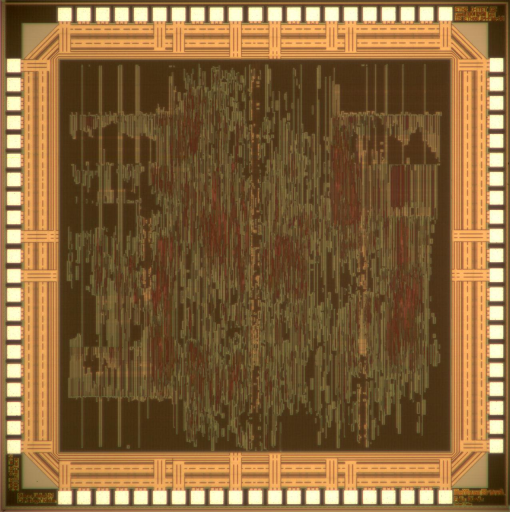

The IIS Chip Gallery

HighDefAudio (2008)

by

| Application | Audio |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 1.8 V |

| Clock | 24 MHz |

Intel's High-Definition Audio (HDA) standard supports the exchange of multi-channel high-resolution audio signals. Up to 16 channels with up to 32 bits per sample at 192 kHz sampling rate can be handled. Independent of the signal's sampling rate, the HDA interface uses a 24 MHz bit clock for the frame-oriented data transfer. The sampling frequency for the conversion to the analog world therefore requires special reconstruction methods.

The aim of this semester project was an ASIC prototype which demonstrates an 8-channel HDA interface that adapts the data streams and clock rates to digital-to-analog converters on the same chip. The task for the students was the design of the HDA interface. Beside the interface control and audio stream management, the sample clock needs to be regenerated to the precise conversion frequency. By only using digital standardcells, for non-rational clock frequencies this can only be achieved by introducing jitter. One task was to minimize this jitter as much as possible.

The sample-rate converter (SRC)-based digital-to-analog converters were provided by Anagram as virtual components (VHDL code). The students implemented the whole system on the chip. Six channels could be placed on the restricted silicon size available to student projects. Tests of the system proved that the converter's quality could be sustained through the HDA interface.