The IIS Chip Gallery

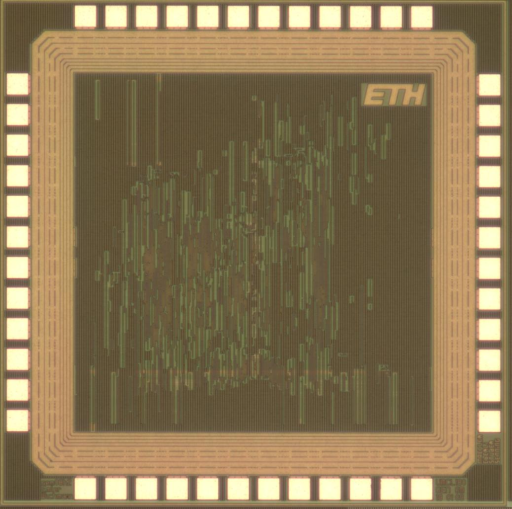

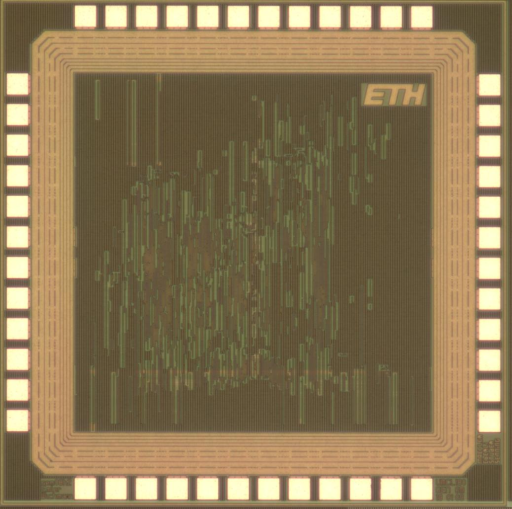

MDP (2008)

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN48 |

| Dimensions | 1525μm x 1525μm |

| Gates | 80 kGE |

| Voltage | 1.8 V |

| Clock | 100 MHz |

Receivers for multiple-input multiple-output wireless communication systems can be designed using different matrix decomposition algorithms. Some of them have been implemented with processor-like architectures controlled by hard-coded finite state machines (FSM). For example, the QR-decomposition and the SVD could be realized with similar architectures and similar computational blocks, but different hard-coded FSMs.

The aim of this project was to implement a processor being able to perform virtually all matrix decomposition algorithms on the same hardware. Hence, all operations required to efficiently calculate the desired matrix decompositions have been identified. Then, a processor with a master-slave CORDIC, extended by an angular unit, a complex-valued multiply-accumulate unit (CMAC), and a general-purpose arithmetic logic unit (ALU) has been implemented. All these computational units are controlled by a programmable state machine. This approach grants high flexibility. It can be used as a reference design for future implementations of dedicated matrix decomposition algorithms.

The matrix decomposition processor has been implemented in 180 nm CMOS technology. The gate count is 75 kGE, approximately 70 percent larger than a dedicated SVD core. The maximal clock frequency is 100 MHz.