The IIS Chip Gallery

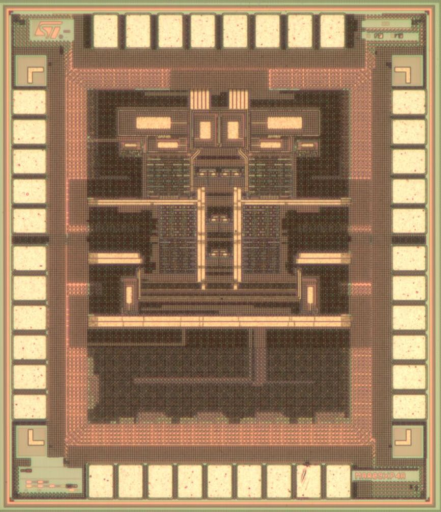

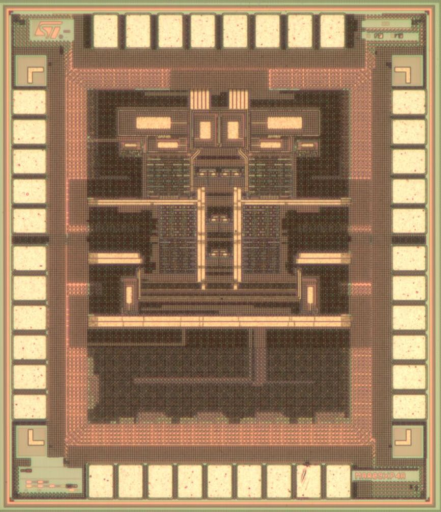

ADC (2009)

by

| Application | Converter |

| Technology | 130 |

| Manufacturer | STM |

| Type | Research Project |

| Dimensions | 900μm x 800μm |

| Voltage | 1.2 V |

| Power | 34.7 mW |

As data-centric application proliferate in both cellular and local area networks, higher data-rate expectations continue to precipitate newer wireless standards, while popular incumbent standards must be retained. From the user's point of view, the current trends call for designs that allow convergence of wireless services, allowing access to different standards from the same wireless device and cost effective solutions for intercontinental roaming. For space and cost reasons, hardware has to be shared as much as possible in this devices.

Reconfigurability of wireless radios, or software defined radio (SDR), has therefore become a focus of recent research. Analog hardware is generally seen as an impediment to adaptability and its reduction a desirable outcome in the quest for SDR, especially as scaling of CMOS down to 100 nm and below increasingly favors digital design over analog. High-performance ADCs are therefore an enabling component in the design of multi-standard radios.

In this research project, a reconfigurable tri-level/multibit multi-mode DS modulator has been implemented in 0.13 um CMOS. The implemented DS modulator covers signal bandwidths up to 20 MHz making it suitable for cellular applications including 4G radio systems, also known as IMT-Advanced, which support scalable RF bandwidths up to 40 MHz. With a maximum sampling rate of 400 MHz, the modulator achieves a DR between 86 dB and 70 dB for signal bandwidths between 100 kHz and 20 MHz, respectively, at a scalable power consumption between 2 mW and 34 mW from a 1.2 V supply.