The IIS Chip Gallery

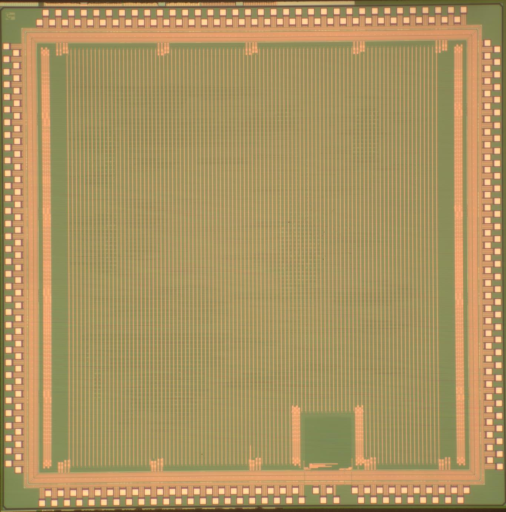

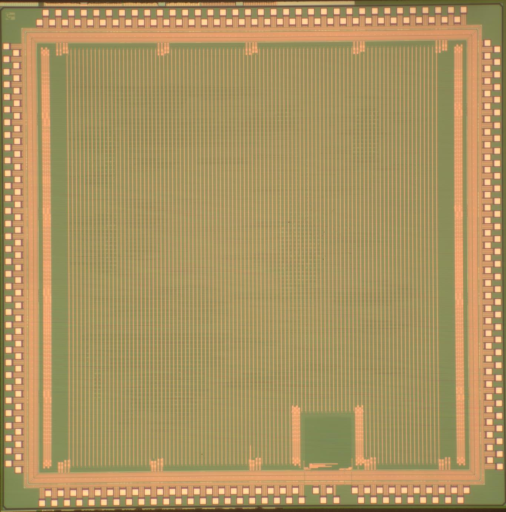

clsn601p (2008)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | PGA208 |

| Dimensions | 5000μm x 5000μm |

| Gates | 1200 kGE |

| Voltage | 1.2 V |

| Clock | 80-320 MHz |

The IEEE 802.11n wireless LAN standard relies on multiple-input multiple-output (MIMO) technology with up to 4 spatial streams to provide high data rates across a wide range with wire-like quality of service. Unfortunately, the circuit complexity of a corresponding MIMO baseband transceiver grows rapidly with the number of spatial streams. Hence, current commercial implementations of IEEE 802.11n support only up to 2 streams with 2 or 3 antennas and are limited to data rates of 300 Mbps.

In this research project, a fully IEEE 802.11n compliant MIMO-OFDM baseband transceiver ASIC was developed. The circuit is the worldwide first implementation of IEEE 802.11n that supports up to 4 spatial streams with a bandwidth of 40 MHz to achieve up to 600 Mbps throughput. The innovative architecture of the industrial-grade design was tailored to efficiently handle the complexity of modern communication standards and is well suited as a basis for a variety of future research projects.

The initial implementation was realized in a 130 nm CMOS technology. The manufactured prototype ASIC employs a soft-output MMSE receiver for MIMO detection. Optimizations on the algorithm and architectural level lead to a core area of the 4-stream transceiver that is almost on par with the area of commercial state-of-the-art 2-stream IEEE 802.11n transceiver ASIC implementations.

The chip features: