The IIS Chip Gallery

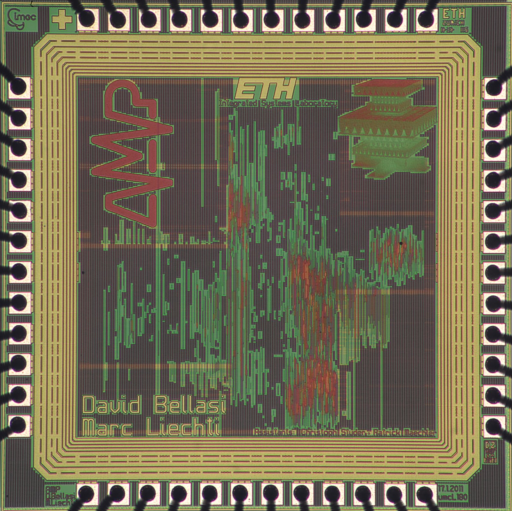

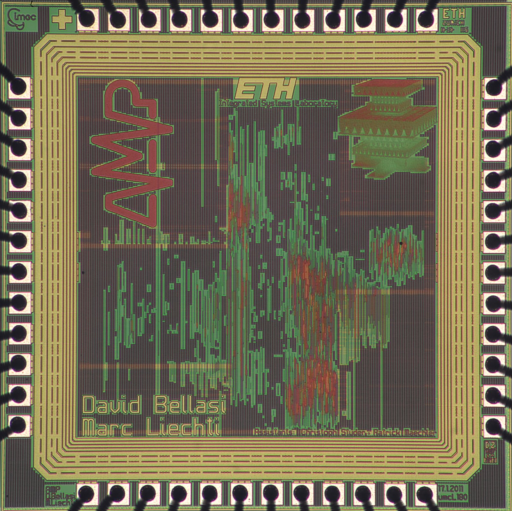

AMP (2011)

Additional pictures below, click to see larger versions

by

| Application | Audio |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 100 kGE |

| Voltage | 1.8 V |

| Power | 80 mW, 140MHz |

| Clock | 140 MHz |

Digital VLSI ASIC design and testing in 180nm CMOS. Implementation of audio restoration employing an iterative thresholding algorithm using Approximate Message-passing (AMP). This algorithm from the field of Compressed Sensing is adapted to remove impulsive noise, such as clicks and pops, from a stream of generic 16-bit audio samples by exploiting the sparsity of audio signals in the frequency domain and of clicks in time domain. The main unit of the implemented AMP architecture performs a fast 512-point Discrete Cosine Transformation and its inverse based upon an efficient complex-valued 256-point Fast Fourier Transform. The design can achieve sample rates above 200kHz at a maximum clock frequency of over 140MHz consuming around 80mW of power.

There is a funny bug with this chip. On the bottom right corner, the date is mistakenly written as 2011, where as when the chip was taped out, it was January 2012.