The IIS Chip Gallery

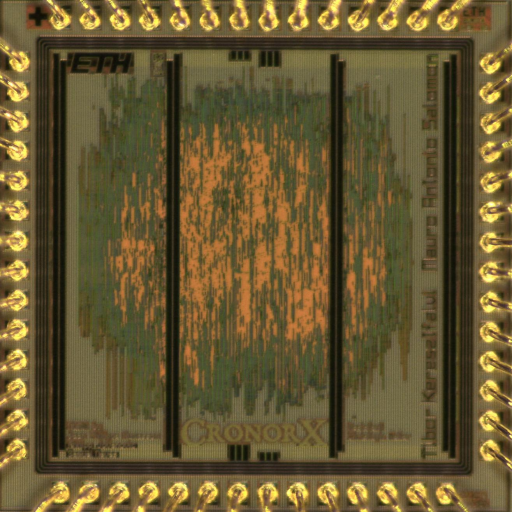

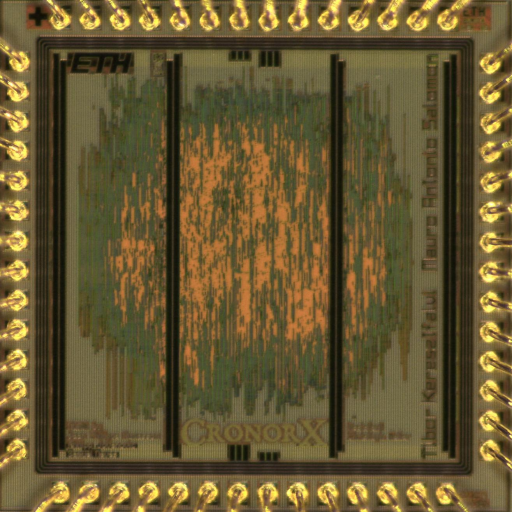

CronorX (2013)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 60 kGE |

| Voltage | 1.8 V |

| Power | 1 mW, 1MHz 1.8V |

| Clock | 125 MHz |

NORX developed by Jean-Philippe Aumasson, Philipp Jovanovic and Samuel Neves is an Authenticated Encryption Algorithm with Associated Data (AEAD) for the CAESAR competition

The chip implements Norx with arbitrary round configurations and both 32 and 64-bit word lengths. However it does not support the various parallelization options.

Since the throughput of this core is very high (>10 Gbps), it conatins an elaborate input stage that allows either full length data input at a reduced operating speed, or re-uses part of the old message to generate an output at full speed (albeit without controlling the entire message). This second mode is obviously uninteresting from a functional view, hoever it helps us to determine the power consumption of the core while running at speed

The name has been derived from Cronus from the Greek Mythology, the last king of the Titans and father of Zeus.

.