The IIS Chip Gallery

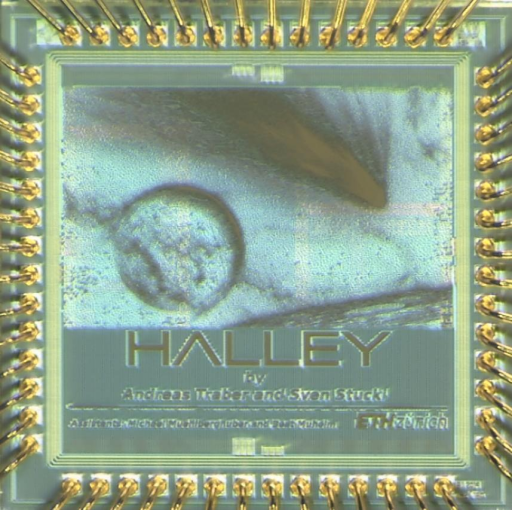

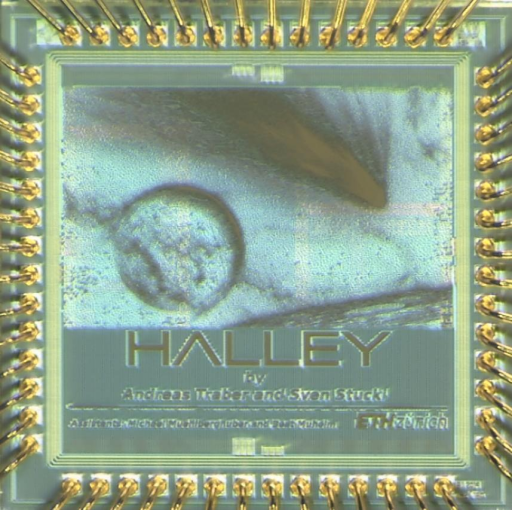

Halley (2013)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 80 kGE |

| Voltage | 1.8 V |

| Power | 70 mW, 167MHz 1.8V |

| Clock | 167 MHz |

Halley is an application-specific instruction-set processor (ASIP) tailored to verify digital signatures according to the Elliptic Curve Digital Signature Algorithm (ECDSA). The instruction set provided by Halley is universal and allows arbitrary calculations in the finite fields required to complete a signature verification as defined in the NIST B-233 standard.

The ASIP builds upon a 16-bit wide shared datapath supporting both the binary- and the prime-field operations needed to complete an ECDSA verification. A two-stage finite-state machine (FSM) controlling hierarchy handles the implemented multi-precision finite-field arithmetic and interacts with a programmable control unit on top. Although the instruction set of this control unit is tailored to ECDSA signature verification, it can also be used to generate digital signatures according to ECDSA.

In order to be able to calculate various algorithms based on the provided finite-field operations, Halley hosts a 2KB dual-port memory for data storage and a 6KB single-port instruction memory. Using Lopez-Dahab projective coordinates in order to represent the elliptic-curve points, the final chip finishes a signature verification in about 1.9Mcycles (depending on the input). This equals to 11ms when running the chip at its maximum frequency of 167Mhz, meanwhile consuming an average power of 70mW.

The same core has been combined with the Open RISC core to form Sir10us. The name alludes to the fact that the comet Halley follows an elliptic curve around the sun