The IIS Chip Gallery

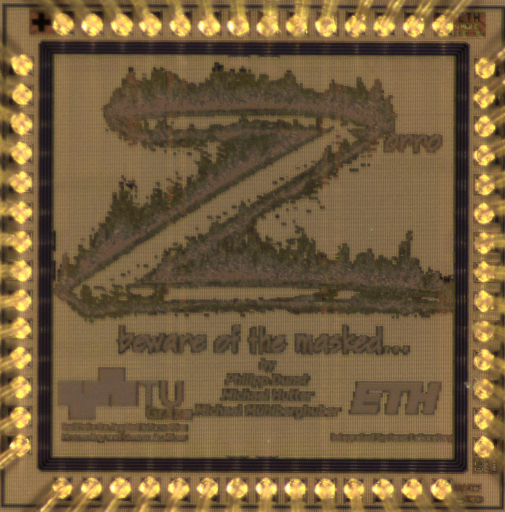

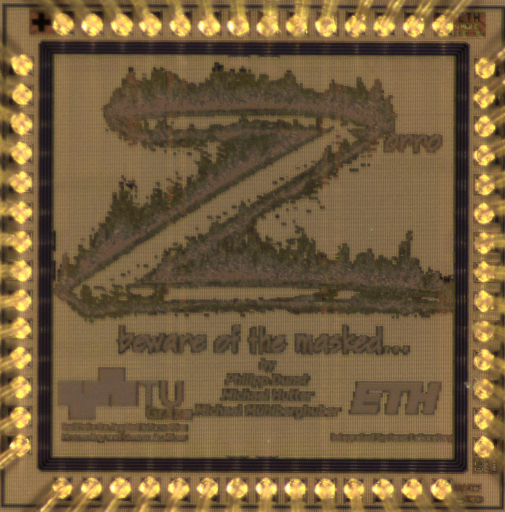

Zorro (2013)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Master Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 50 kGE |

| Voltage | 1.8 V |

| Power | 1 mW, 1MHz 1.8V |

| Clock | 200 MHz |

Zorro was designed to evaluate different counter measures against Differential Power Analysis Attacks (DPAs). Three different implementation are combined on one chip. Therefore, the chip can run in several modes of operation:

Zorro was designed to compare and evaluate state of the art DPA countermeasure techniques. It contains three independent implementations of an authenticated encryption system. It is based on the Keccak permutation and the duplex construction. It uses a state of 1600 bits and can observe 1024 bits each round. The implementations differ only because of the secret sharing process. They are called

This is another chip that has been designed as part of our long standing collaboration with the IAIK of TU-Graz

.