The IIS Chip Gallery

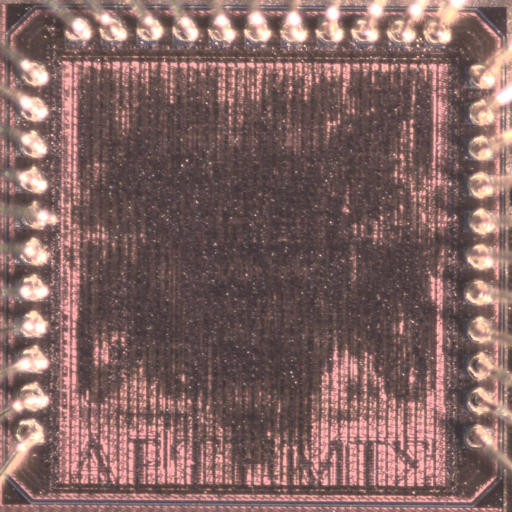

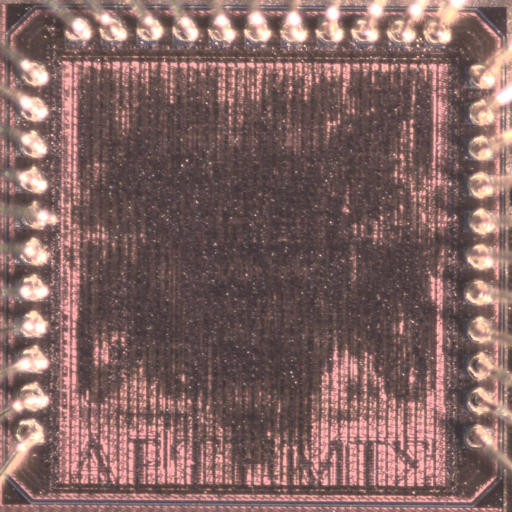

Artemis (2014)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 600 kGE |

| Voltage | 1.2 V |

| Power | 1 mW @1.2V 1MHz |

| Clock | 500 MHz |

This is one of a series of four chips that is part of the PULP project which add various floating point operations to a cluster of 4 processors.

All four chips use the same basic PULP architecture with 4 Or10n cores, 16 kBytes of L2 memory, 16 kBytes of TCDM memory organized into 8 banks and a total of 4 kBytes of instruction cache. The difference is how the floating point units are added to the system.

Artemis, is the base version, which adds a dedicated FPU to each core that is compatible to the single precision (32bit) IEEE-754 standard (excluding some rounding modes). It can perform floating point additions and multiplication with 2 cycles of latency and contains no soft IPs.

The names have been chosen from the mythology. According to some telling of the stories of the Greek mythology, Artemis (the goddess of hunting and virginity) was in love with Orion, but ends up killing him. A reference to the core Or10n.