The IIS Chip Gallery

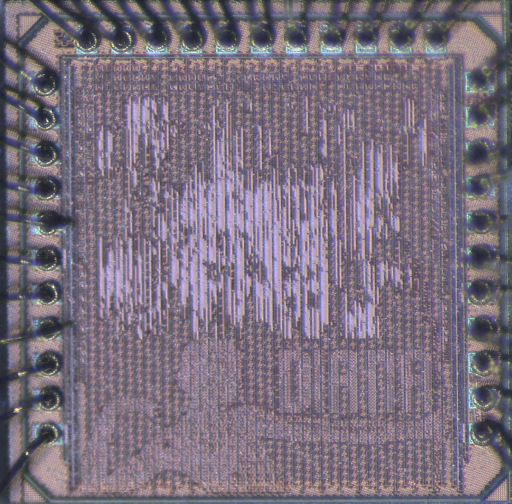

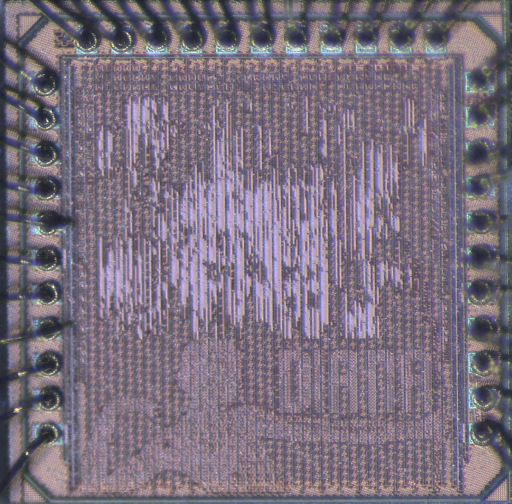

Diana (2014)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Research |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 600 kGE |

| Voltage | 1.2 V |

| Power | 1 mW @1.2V 1MHz |

| Clock | 500 MHz |

This is one of a series of four chips that is part of the PULP project which add various floating point operations to a cluster of 4 processors.

All four chips use the same basic PULP architecture with 4 Or10n cores, 16 kBytes of L2 memory, 16 kBytes of TCDM memory organized into 8 banks and a total of 4 kBytes of instruction cache. The difference is how the floating point units are added to the system.

Diana, is very similar to Artemis, it contains four cores each with a dedicated FPU. However, for each core a slightly different FPU is used. One core uses a standard FPU identical to the one used in Artemis, the remaining three feature inexact adders and multipliers in the FPU pipeline, in order to trade-off area/power versus precision. This work was done by the IC-LAB of EPFL as part of the IcySoC Nano-Tera project. Details about the inexact arithemtic units can be found on the IC-LAB, inexact page.

The names have been chosen from the mythology. Diana is frequently associated with Artemis in the Roman mythology, is also considered a moon goddess and, as in the logo of this chip, is frequently depicted with a bow. Using a god from the Roman pantheon also makes sense, as EPFL is the sister university of ETH Zurich in the French speaking part which has its roots also due to Roman settlements in that area.