The IIS Chip Gallery

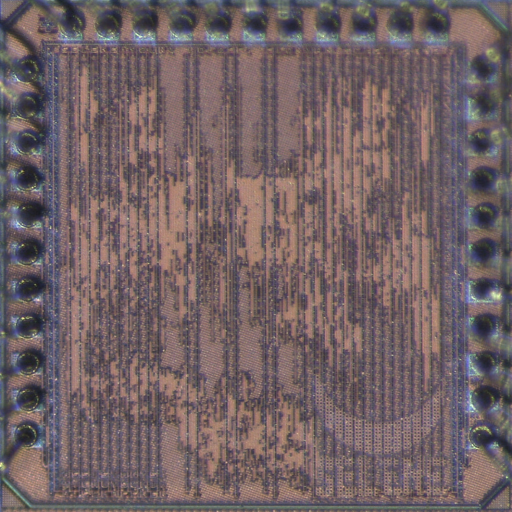

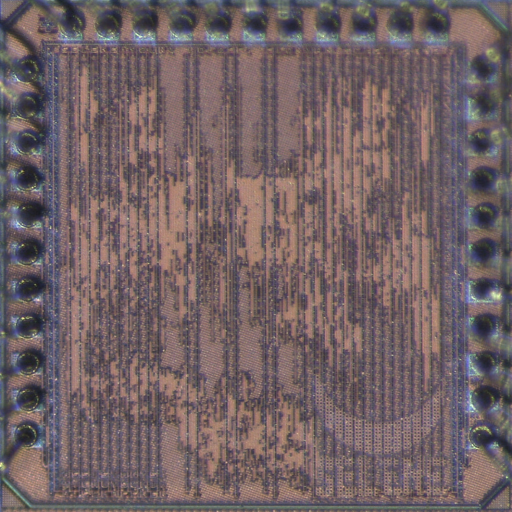

Selene (2014)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 600 kGE |

| Voltage | 1.2 V |

| Power | 1 mW @1.2V 1MHz |

| Clock | 500 MHz |

This is one of a series of four chips that is part of the PULP project which add various floating point operations to a cluster of 4 processors.

All four chips use the same basic PULP architecture with 4 Or10n cores, 16 kBytes of L2 memory, 16 kBytes of TCDM memory organized into 8 banks and a total of 4 kBytes of instruction cache. The difference is how the floating point units are added to the system.

Contrary to all the other chips, Selene uses a different number representation for the floating point numbers. In this Logarithmic Number System, some traditionally difficult operations such as multiplication and division can easily be calculated, while otherwise simple operations such as additiona dn subtraction become more challenging. The FPU used in Selene implements a LNS based FPU that has the same precision as single precision IEEE-754 floating point units implemented for the other chips. As this LNS based FPU is much larger only one instance of the FPU is shared by using the same infrastructure in Hecate. However, although only one FPU is instantiated, since multiplication and division can be performed at the cores directly, Selene can actually perform 5 Flops at the same time (4 within the cores and 1 in the FPU), where as Artemis and Diana manage at most 4 and Hecate, only 2.

The names have been chosen from the mythology. In the Greek Mythology, three godesses have traditionally been associated with the moon: Artemis, Hecate and Selene. This connects this name to the other two chips. The logo contains a crescent moon, to show the association with the moon. Additionally, the name Selene contains the letters LNS that stand for the logarithmic number system.