The IIS Chip Gallery

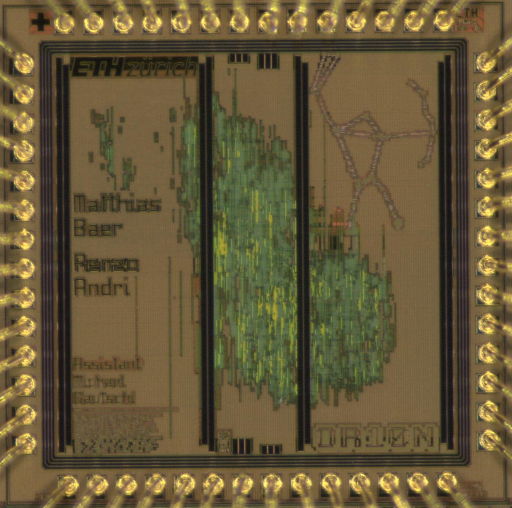

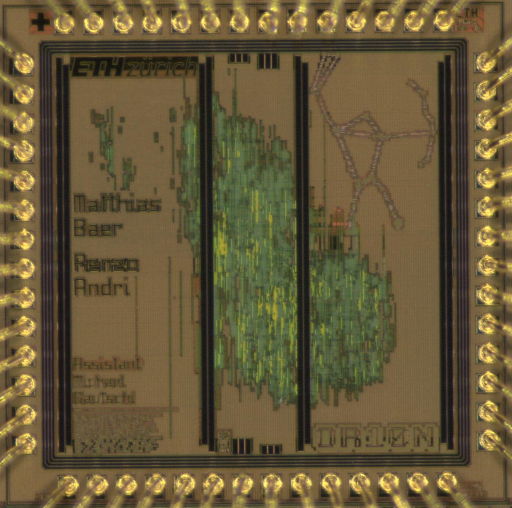

Or10n (2013)

Additional pictures below, click to see larger versions

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 80 kGE |

| Voltage | 1.8 V |

| Power | 1 mW, 1MHz 1.8V |

| Clock | 360 MHz |

This chip implements the Open RISC core. It is a fresh implementation that does not reuse the code from the Open RISC repository and it has been optimized for ASIC implementations. Various improvements have increased the IPC on typical applciations to above 0.9.

This is the first semester thesis project at the IIS that has been developed using System Verilog instead of VHDL.

The same core has also been used in the Sir10us design from this run, with slightly different memory configuration.

The logo on the top right represents the constellation of Orion.