The IIS Chip Gallery

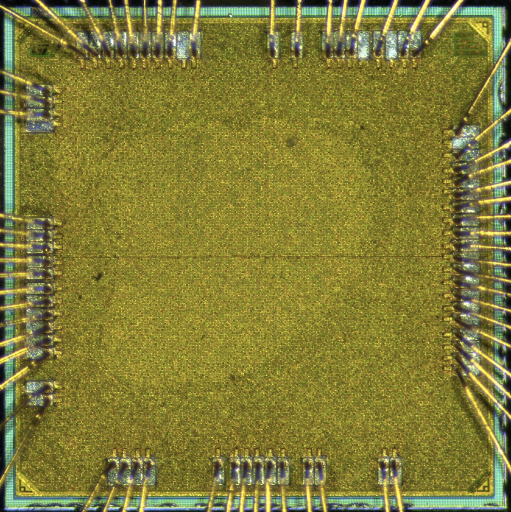

Pulp (2013)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 28 |

| Manufacturer | STM |

| Type | Research |

| Package | QFN64 |

| Dimensions | 1650μm x 1650μm |

| Gates | 700 kGE |

| Voltage | 0.4-1.2 V |

| Power | 8 mW @0.7V, 10MHz |

| Clock | 475 MHz |

Parallel Ultra Low power Processor (PULP) is a shared data memory, parallel processor architecture. This version of the chip was implemented using ST28 FDSOI technology, using lower leakage RVT transistors and contains one cluster with 4 OpenRISC cores modified to have much higher IPC and a dedicated DMA controller.

The chip has been designed to test aggressive body biasing techniques especially to reduce the leakage current during periods of inactivity. The system includes 6 power islands that can be switched between two external body bias voltages in a short period of time.

The chip has been designed in collaboration with University of Bologna and ST Microelectronics Grenoble

The chip was tested extensively on our HP93000 tester and was fully functional.

A new version of the family is Pulp v2