The IIS Chip Gallery

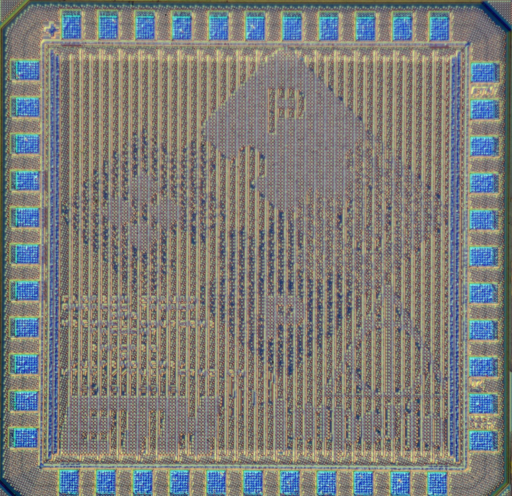

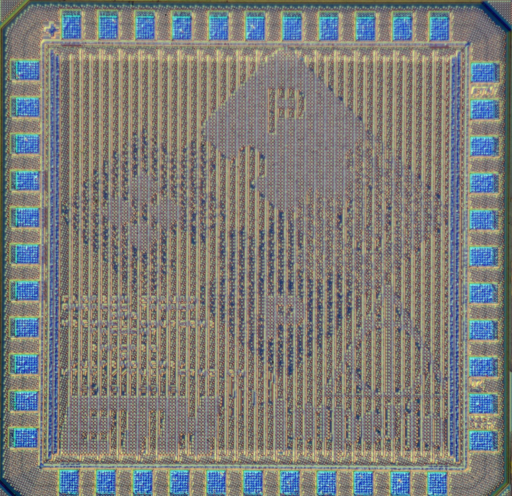

Imperio (2015)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 500 kGE |

| Voltage | 1.2 V |

| Power | 32.8 mW @1.2V 400MHz |

| Clock | 650 MHz (typ) MHz |

PULPino is an open-source microcontroller like system, based on a small 32-bit RISC-V core that was developed at the Integrated Systems Laboratory of ETH Zurich. The core has an IPC close to 1, full support for the base integer instruction set (RV32I), compressed instructions (RV32C) and partial support for the multiplication instruction set extension (RV32M). It implements our non-standard extensions for hardware loops, post-incrementing load and store instructions, ALU and MAC operations. To allow embedded operating systems such as FreeRTOS to run, a subset of the privileged specification is supported. When the core sits idle, the platform can be put into a low power mode, where only a simple event unit is active and wakes up the core in case an event/interrupt arrives.

Imperio is the first ever ASIC implementation of PULPino in UMC 65nm. It has full debug support on all targets. In addition we support extended profiling with source code annotated execution times through KCacheGrind in RTL simulations.

The SoC features a rich set of peripherals such as an UART, I2C, SPI Master and GPIO amongst others.

PULPino is based on IP blocks from the PULP project, the Parallel Ultra-Low-Power Processor that is developed as a collaboration between multiple universities in Europe, including the Swiss Federal Institute of Technology Zurich (ETHZ), University of Bologna, Politecnico di Milano, Swiss Federal Institute of Technology Lausanne (EPFL) and the Laboratory for Electronics and Information Technology of Atomic Energy and Alternative Energies Commission (CEA-LETI).

The name comes from the Harry Potter series of books, where Imperio is one of the three forbidden curses. In theory we could make two more chips from this series.

You can see Florian presenting his updates on Imperio in the following Youtube video at the 5th RISC-V Workshop.