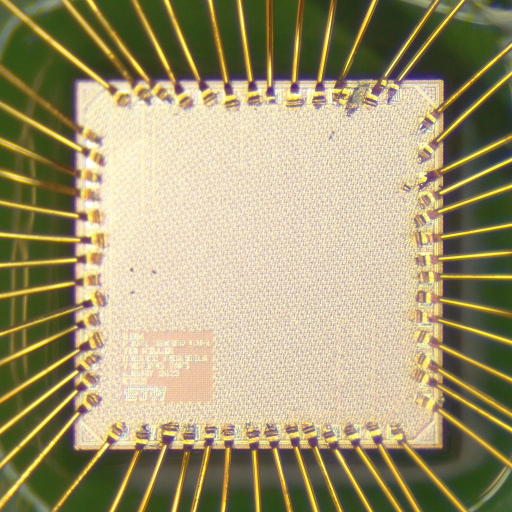

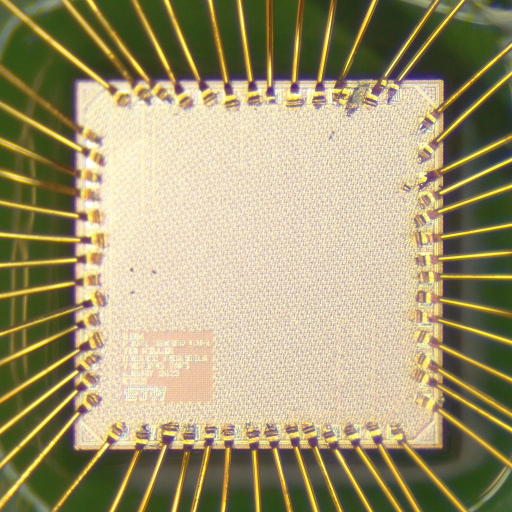

The IIS Chip Gallery

Bern (2023)

by

| Application | Low-power |

| Technology | 22 |

| Manufacturer | GF |

| Type | Research |

| Package | Baredie |

| Dimensions | 1250μm x 1250μm |

| Voltage | 0.8 V |

| Power | 1.38μW |

This chip implements a fully discrete-time charge domain bridge-to-digital converter for implantable force sensing after a spinal fusion surgery. We propose an energy-efficient RC bridge to replace the quarter bridge, reducing power consumption. Further, the sampling capacitor in the bridge is reused in a series-parallel amplifier (SPA) and charge-injection successive approximation (CI-SAR) analog to digital converter, thus saving power consumption and reducing the noise. Implemented in 22nm CMOS, the proposed design achieved an SNR of 55.3dB while consuming 1.38 μW at 10ksps with the lowest reported FoM of 0.29pF/step and the smallest area of 0.07mm^2.