The IIS Chip Gallery

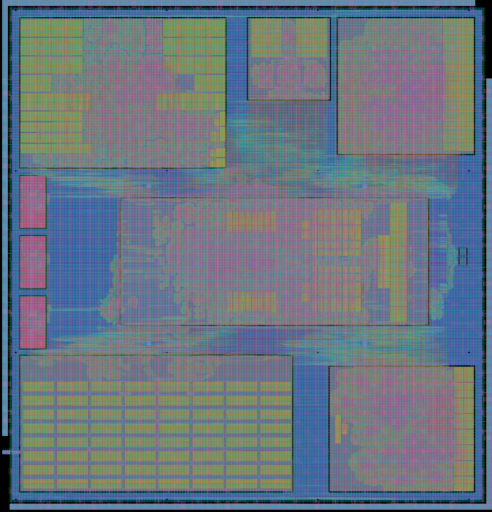

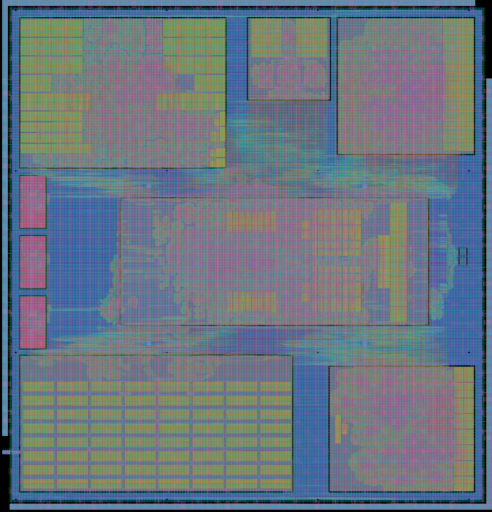

Carfield (2023)

Additional pictures below, click to see larger versions

by

| Application | Pulp |

| Technology | 16 |

| Manufacturer | Intel |

| Type | Research Project |

| Package | BGA1733 |

| Dimensions | 4085μm x 3925μm |

| Gates | 70 MGE |

| Voltage | 0.8 V |

| Power | 450 mW @ 0.8 V, 600 MHz |

| Clock | 400-600 MHz |

Carfield is the first prototype in the advanced Intel16 FinFet technology of our Open-Research platform for safety, resilient and time-predictable systems.

The rapid evolution of AI algorithms, the massive amount of sensed data and the pervasive influence of AI-enhanced applications across application-domains like Automotive, Space and Cyber-Physical embedded systems, call for a paradigm shift from simple micro-controllers towards powerful and heterogeneous edge computers in the design of next generation of mixed-criticality systems. These must not only deliver outstanding performance and energy efficiency but also ensure steadfast safety, resilience, and security.

The Carfield SoC aims to tackle these architectural challenges establishing itself as a pre-competitive heterogeneous platform for mixed-criticality systems, underpinned by fully open-source Intellectual Properties (IPs). The SoC showcases pioneering hardware solutions, addressing challenges related to time-predictable on/off-chip communication, robust fault recovery mechanisms, secure boot processes, cryptographic acceleration services, hardware-assisted virtualization, and accelerated computation for both floating-point and integer workloads.

The foundational architecture of Carfield revolves around two asymmetric computing domains:

The secure domain, based on the OpenTitan project, serves as the Hardware Root-of-Trust, handling secure boot procedures, system integrity monitoring, and cryptographic acceleration services.

To augment computational capabilities, Carfield incorporates two general-purpose accelerators: the spatz cluster, which handles vectorizable multi-format floating-point workloads (down to FP8), and the HMR 12-cores Integer Cluster, specialized in executing reliable boosted Quantized Neural Network (QNN) operations, exploiting the HMR technique for rapid fault recovery and integer arithmetic support in the ISA of the RISC-V cores from 32-bit down to 2-bit and mixed-precision formats.

The system's interconnect relies upon a 64-bit Advanced eXtensible Interface (AXI) Crossbar (XBAR), enriched with time-predictable communication properties.

A full set of peripherals, including SPI, I2C, Serial Link, CAN FD, HyperBUS, and timers, including watchdogs, complete the features of the SoC.