The IIS Chip Gallery

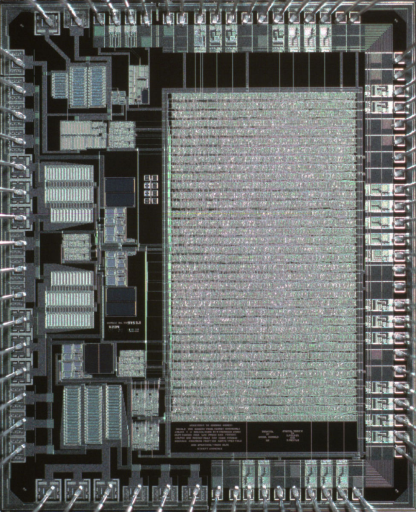

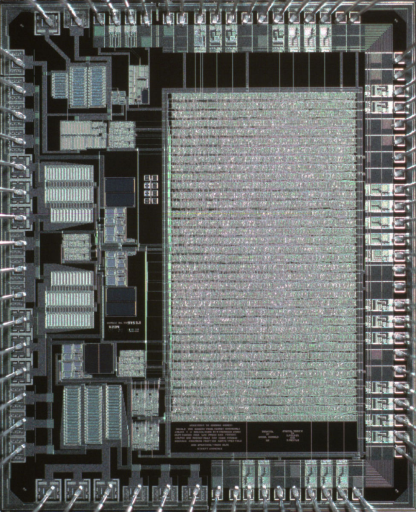

THROXTIL (1998)

by

| Application | Graphics |

| Technology | 800 |

| Manufacturer | austriamicrosystems |

| Type | Research |

| Package | PGA100 |

| Dimensions | 3900μm x 4700μm |

| Voltage | 5 V |

| Clock | 200 MHz |

For the miniaturized high-resolution CCD Camera a chip set is being developed by the Integrated Systems Laboratory. THROXTIL is one of the ASICs for the camera head. It contains the clock receiver, the programmable CCD pulse generator, the parameter link interface and parts of the driver stage.

The THROXTIL ASIC has been designed and integarted in a high-voltage process (AMS/THESYS HV CMOS 0.8um). The clock receiver generates a 200 MHz 5V clock from a differentail +- 100mV input signal. The pulse generator sequences are freely programmable over the parameter link with a resolution of 500ps. The on chip driver stages convert the CMOS-level pulses to the different required voltage levels with the necessary high-current drive capabilities. The verification of the 3.9mm x 4.7mm chip has been performed with the ASIC tester HP83000. Additional tests to verify the functionality of the internal nodes were done by probing internal voltages. The clock receivers maximal data rate is beyond 666 Mbit/s.