The IIS Chip Gallery

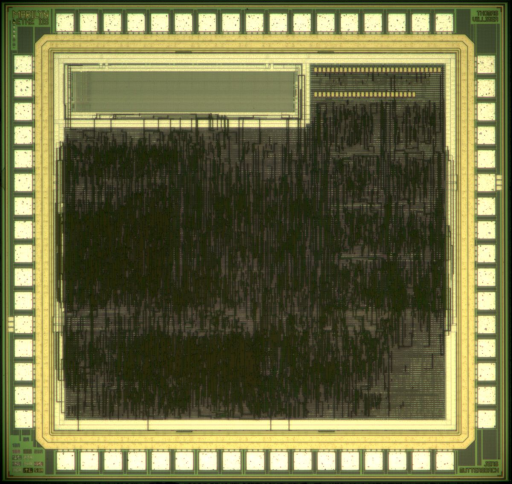

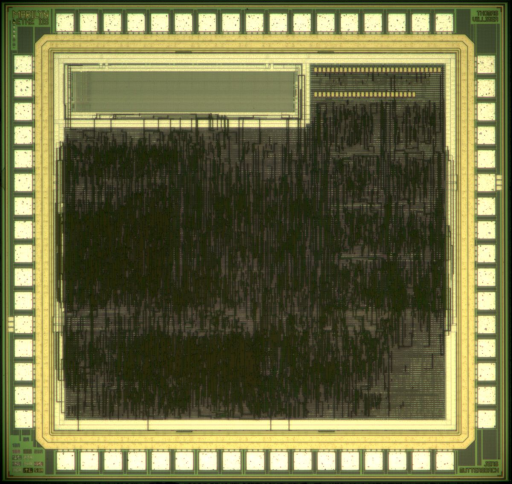

Marilyn (2000)

by

| Application | Cryptography |

| Technology | 250 |

| Manufacturer | STM |

| Type | Research |

| Package | LCC68 |

| Dimensions | 2000μm x 2100μm |

| Voltage | 2.5 V |

| Clock | 280-550 MHz |

To verify the Globally-Asynchronous Locally-Synchronous (GALS) design methodology a complete chip was implemented in this technique. A secret-key iterated block-cipher algorithm called SAFER was chosen as application. SAFER stands for Secure And Fast Encryption Routine, an algorithm invented by James Massey at ETH. Information is encrypted or decrypted in data blocks of 8 bytes by repeatedly applying the algorithm in up to 12 rounds. The implementation supports the currently strongest version, SK-128, that employs a strengthened key scheduling based on a 128-bit key. The chip supports four cryptographic modes: ECB, CBC, CFB and OFB.

The partitioning chosen mainly reflects the inherent functional groups of the system. The implementation ends up in having five different clock domains, several lookup-tables, an asynchronous RAM, and an asynchronous FIFO that serves as feed-forward buffer and is an example for a completely asynchronous block included in the GALS environment.

The chip called Marilyn was fabricated in a 0.25 um 5-metal technology and compared to a strictly synchronous counterpart processed on the same wafer. A data throughput up to 780 MBit/s was obtained in the GALS version and an energy saving of 25% compared to the already power-optimized synchronous version was achieved.

See also Merlin, the synchronous version of this chip. More information on GALS can be obtained through our GALS page.