The IIS Chip Gallery

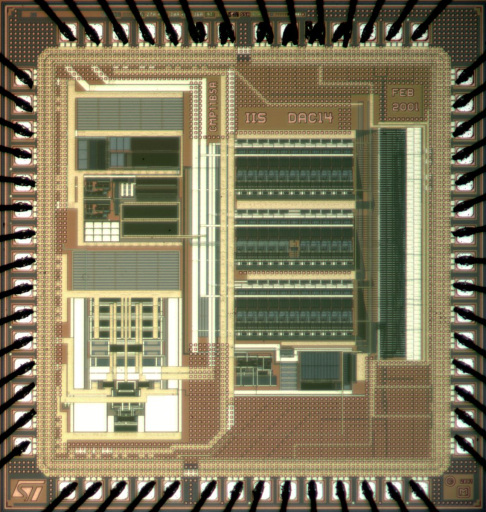

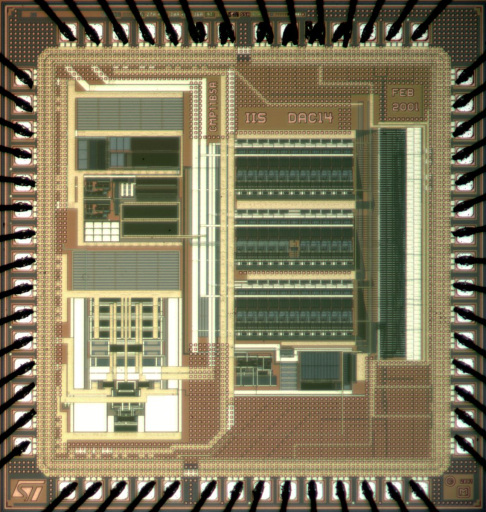

DAC14 (2001)

by

Wireline communications services such as ADSL, VDSL or powerline communications systems provide high data rates by using already existing cable connections to the customer premises. In contrast to special high-speed wiring such as coaxial cable or fiber connections, the physical bandwidth that is available for transmitting the data is limited in this case. Therefore sophisticated modulation schemes are used to be capable of providing high data rates. The implementation ofthese modulation schemes requires high linearity and high spurious free dynamic range ofthe A/D and D/A converters that finally convert the signal from the digital to the analog domain and vice versa. This is the reason why the new wireline communications services are one ofthe driving forces behind the current research effort of new data converters.

For D/A converters, resolutions in the order of14 bits at conversion rates ofup to 100 Msample/s are required in the head-ends ofwire-based communications systems. This accuracy normally cannot be obtained by pure matching ofpassive or active devices, therefore on-chip calibration has to be used.

The D/A converter implemented in this project utilizes a completely floating current source that allows the measurement and calibration ofthe unit current while in full operation and thus provides a true background calibration. The actual calibration ofthe thirty-two current sources forming the five most significant bits is performed by an analog feedback loop. The D/A converter is implemented in an advanced digital 0.25um single-poly CMOS process with six layers of metal. The achieved resolution with on-chip calibration is 14 bits with a maximum update rate of 50 Msample/s.

See DAC14 (2003) for another version of this chip.