The IIS Chip Gallery

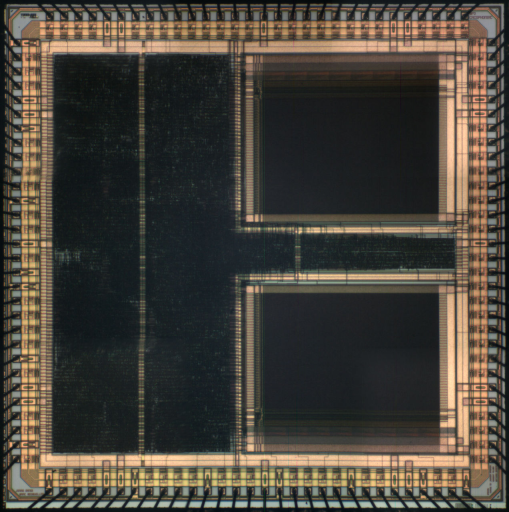

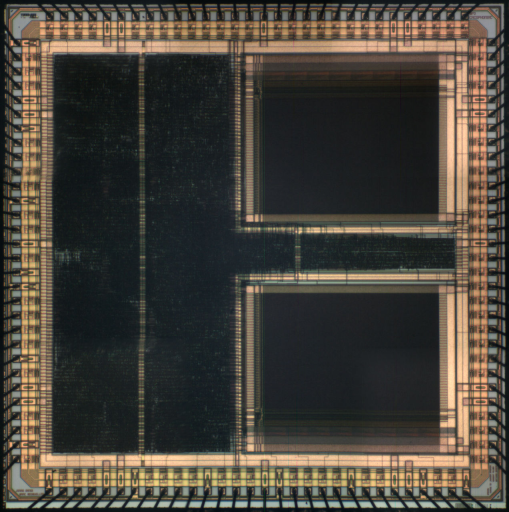

MP3 (2001)

by

| Application | Audio |

| Technology | 600 |

| Manufacturer | austriamicrosystems |

| Type | Semester Thesis |

| Voltage | 3.3 V |

Digital Signal Processing part

This circuit receives the decoded spectral components and the side information from the decoder.

The module re-quantizes the spectral data according to the sideband information, reorders them, and performs the joint stereo processing. After the alias reduction the Inverse Modified Discrete Cosine Transform (IMDCT) resynthesizes the time-domain samples of the narrow frequency bands. Finally, these samples get re-combined to the final PCM signal by the poly-phase filter bank.

Decoder PartThe circuit reads MPEG1 audio layer III standard (ISO/ IEC11172-3) audio data form a SmartMediaTM storage device.

The compressed spectral audio data and control information (header data and scale-factors) are extracted. Subsequently, the audio data is Hoffman decoded. The decoded data with all control information is buffered in an internal memory and read by the DSP part for audio signal processing. After signal processing the PCM audio data is returned and transferred via an I2S interface to an external A/D converter. The external A/D converter is controlled and supplied with clocks to support three different sampling frequencies. A controller manages and coordinates all processing blocks of the decoding process. The complete MP3 decoder does not require any additional external memories.

An external user interface provides the basic capabilities to control the MP3 player chip. It consists of five different signals: Skip Backward, Skip Forward, Play, Break and Stop.

The Project was an experiment of realizing the MP3 decoder as dedicated hardware in silicon in order to explore the potential of this solution in comparison to the commonly realized digital signal processor implementation. It has shown that the algorithm is not at all optimal for integration as dedicated circuit. The large amount of required buffer memories and the huge number of operation modes are the major drawback. The algorithm could be considerably optimized in both silicon area and energy dissipation, however at the cost of violating the standard.

Since this was a VLSI education project, the signal processing chip has been designed to the end and sent for fabrication. After return it has been tested by the students. It showed full functionality.