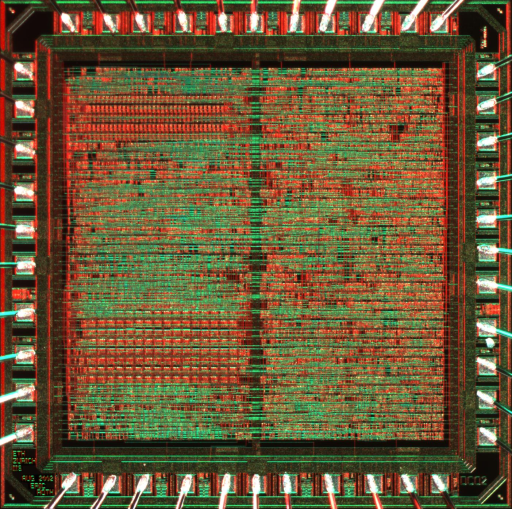

The IIS Chip Gallery

DCO (2002)

by

| Application | Test |

| Technology | 600 |

| Manufacturer | austriamicrosystems |

| Type | Reserach Project |

| Package | LCC44 |

| Voltage | 3.3 V |

The growing popularity of digital multimedia consumer equipment increases the demand for an interconnectivity network between these devices. Distribution of real-time multimedia data over such a network requires alignment of data rates at the sending and receiving nodes to prevent data losses due to buffer overflows or underflows.

Phase-Locked Loops (PLL) are commonly used to synchronize phase and frequency of sampling events to a reference clock. Conventional PLLs employ an analog VCO which cannot be fully integrated in digital standardcell designs. The digital implementation of phase detector, loop filter, and clock dividers is straightforward, whereas a digital substitute for the analog VCO is a challenging problem. In this project, a digitally controlled oscillator (DCO) consisting of digital standardcells only has been developed. Based on a crystal clock, the position of every DCO clock edge is pre-calculated. A delay line shifts this edge to the predetermined position. In order to provide high resolution on limited space, it consists of coarse-and fine-delay elements. To track process, temperature, and voltage variations, two identical reference delay lines are used for calibration.