The IIS Chip Gallery

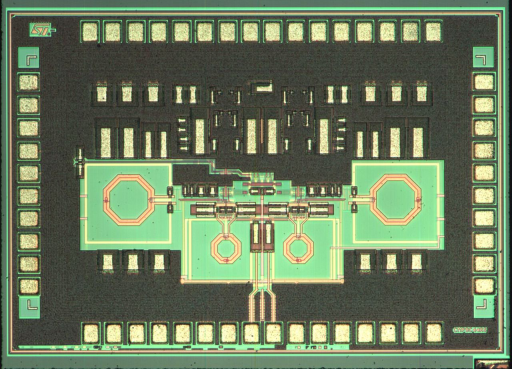

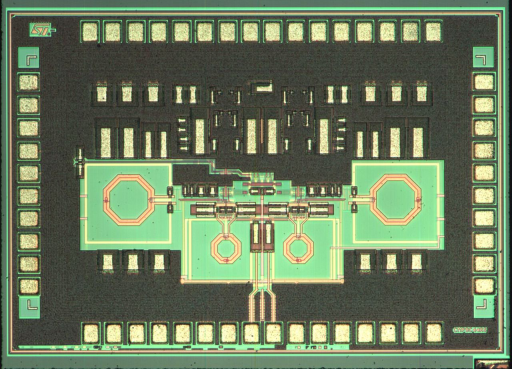

IQ_demod (2003)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | STM |

| Type | Research |

| Package | LCC84 |

| Voltage | 1.2 V |

In the last years the direct conversion architecture has become the architecture of choice mobile communications terminals. It avoids the image suppression problem and allows higher integration by reduction of bulky external components at the price of harder building blocks specifications.

In a WCDMA mobile terminal both the transmitter and the receiver operate simultaneously. Because the attenuation of the transmit signal to the RF receiver is moderate it usually presents the largest blocking signal for its own receiver. In a direct-conversion receiver the transmitter leakage leads to distortion of the baseb-band signal by the non-linearity of the receiver. So very high nonlinearity requirements have to be fulfilled. Especially the second order non-linearity, usually expressed as second order intercept point iIP2, must be in the order of +60dBm or higher. A way to relax the I/Q demodulator's second-order nonlinearity requirements is to provide additional transmitter leakage attenuation by using an external SAWfilter before the I/Q demodulator. However, the price of this approach is reduced receiver integration and increased overall chip cost.

In the first part of this project an in-depth analysis of the second-order product generation in the I/Q demodulator has been worked out. As a result, the main design tradeoffs have been identified and a set of design equations has been established. Then an I/Q Demodulator with high iIP2 has been realized. The circuit is implemented in a standard 0.13um digital CMOS technology with 1.2V supply. The latter imposes special constraints on the circuit design, because it is very difficult to process the large blocking signal with the low headroom given by the stack of 2 or 3 transistors.