The IIS Chip Gallery

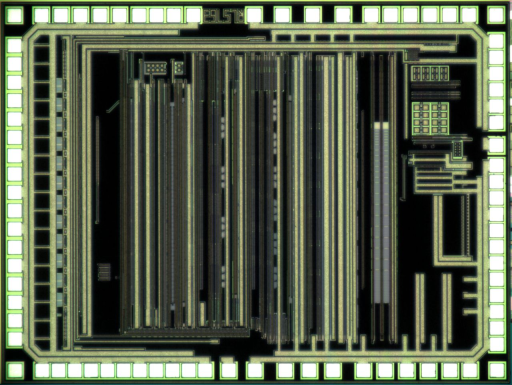

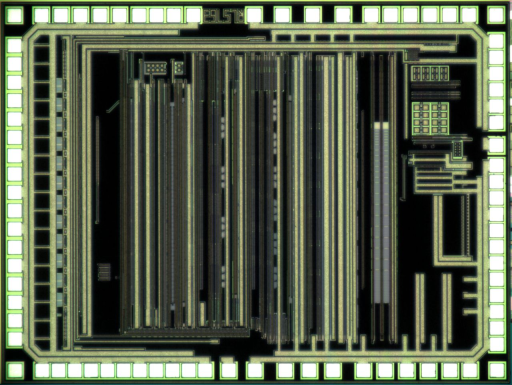

RLS763 (2003)

by

| Application | Converter |

| Technology | 180 |

| Manufacturer | STM |

| Type | Research Project |

| Package | LCC84 |

| Voltage | 1.8 V |

| Power | mW |

Generally folding and interpolating analog-to-digital converters are capable of providing high conversion rates at reasonable power consumption. The main drawback of this architecture is the limited accuracy, which is dominated by the high mismatch of fast differential pairs in CMOS technology.

The scope of this project was to demonstrate the feasibility of folding and interpolation analog-to-digital converters for higher than 7..8bit accuracy. In order to achieve this goal, a calibration scheme, which eliminates the offset voltages of the differential pairs, has been developed and embedded into a 10bit, 125MSamples/s ADC.

ADCs are usually integrated together with a substantial part of the digital back-end. Therefore a mainstream 0.18 um digital CMOS technology with one poly layer, six metal layers, high ohmic resistors and metal-insulatormetal capacitors has been used for this design.