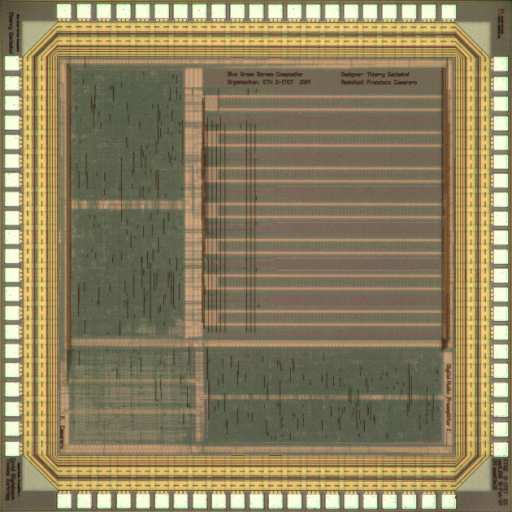

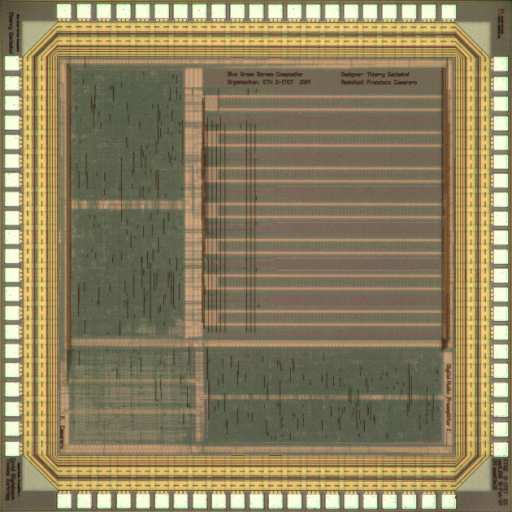

The IIS Chip Gallery

BG_preamp (2004)

by

| Application | Graphics |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 3500 kGE |

| Voltage | 2.5 V |

| Power | 24.75 mW, 27MHz, 2.5V (BG) |

| Clock | 253 MHz (BG), 237MHz (Preamp) MHz |

This chip contains two separate designs due to cost reasons

Blue/Green Compositing ASICThe first compositing in History was made in 1857. The photographer Oscar G. Rejlander took 32 different pictures and composited them together. In the beginning of motion pictures compositing was done by two different methods: either filming in front of a screen were another movie was projected, or by partially exposing the film negative to light, and later exposing the other part. The principal reason for using composites is to save costs, or because it would be impossible to film a scene as such, e.g. space ship movies.

This project implemented a real-time compositing ASIC that takes two ITU-R BT.656 video streams (background and foreground), extracts the foreground object from the constant (green or blue) background in the foreground video stream using a color difference method, and composites it over the background video stream to output a new ITU-R BT.656 compatible video stream (composite).

Internal color space conversions from YCrCb to RGB and back, and several other operations (matte refine, despill, color match, subsampling, etc.) are implemented and user configurable in order to enhance the quality of the composite depending on the situation.

The design has been successfully integrated in a 0.25 \u03bcm standard CMOS technology on a multi-project die that contained one additional student project and the corresponding de-/multiplexing logic for the I/O pads.

Digital Audio Stereo PreamplifierThe aim of this semester project was the design of a digital audio preamplifier chip. The main task of such a preamplifier is to give the user the choice among different digital and analog audio sources at its input. Usually preamplifiers do not contain complex digital signal processing. This design contains only a de-emphasis filter, volume and balance adjustment. For further demands, the chip features an additional interface to perform more sophisticated digital signal processing externally. Stereo data are input and output via common I2S interfaces with 24 bit resolution and 96 kHz sampling frequency.

The user interface provides knobs for the input selection, volume and balance adjustment. The input selection knob allows to choose from a set of four analog and four digital inputs. The external filter loop can be disabled or enabled by a switch. For digital recording, a selected digital input source can be fed out directly. LED bars are supported to display the input and output levels as well as the positions of the volume and balance knobs.

The ASIC provides all the needed control signals for the externally required chips. Those include AD, DA and sample rate converters as well as digital audio interfaces (AES/EBU and SP/DIF, respectively).

The chip has been fabricated in UMC0.25um CMOS technology. The design runs at 24.576 MHz.