The IIS Chip Gallery

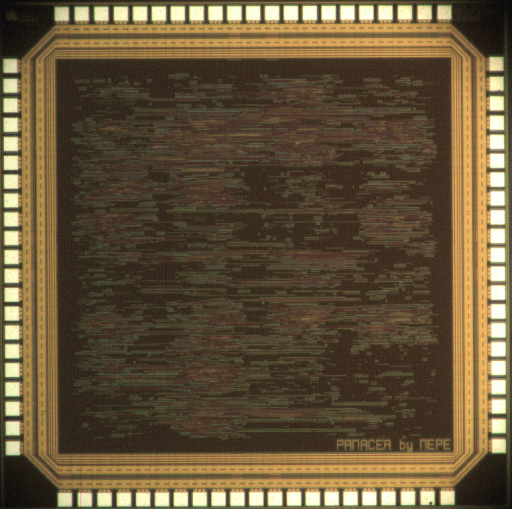

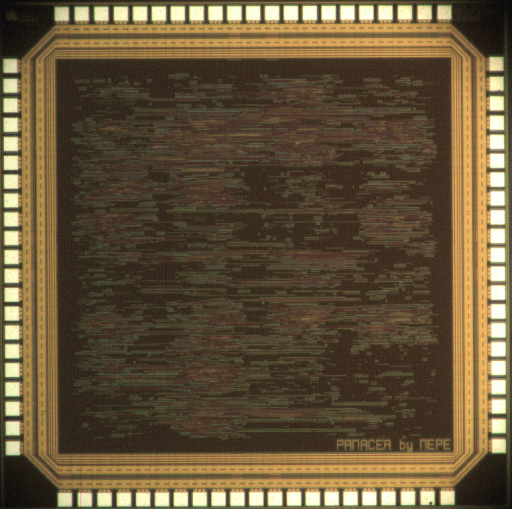

Panacea (2005)

by

| Application | Processor |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 120 kGE |

| Voltage | 2.5 V |

| Clock | 100 MHz |

As layout densities increase with every generation of integrated circuit technology, a growing number of functional modules can be integrated on a single chip. So far the communication between these components was usually based on simple shared bus architectures. Unfortunately, with increasing system complexity, these shared interconnections tend to become the main system bottleneck. As a possible solution, network architectures as known from computer systems were proposed for on-chip communication. This concept is referred to as Network-on-Chip (NoC). The functional blocks are extended by a (standardized) network interface that packetizes the data to be transmitted and a dedicated network in charge of routing data packets is established.

The NOSTRUM architecture designed at the KTH Sweden was taken as basis for this NoC implementation. The communication network is organized as a rectangular mesh, each node of which has a switch that is responsible of forwarding incoming packets according to a hot-potato stress-sensitive routing algorithm. The users of the network, called resources, are also connected to the switches. In order to maximize the number of integrated instances, the complexity of the resources was kept to a minimum. They are designed to generate random data traffic patterns and to collect statistical information on the network performance.