The IIS Chip Gallery

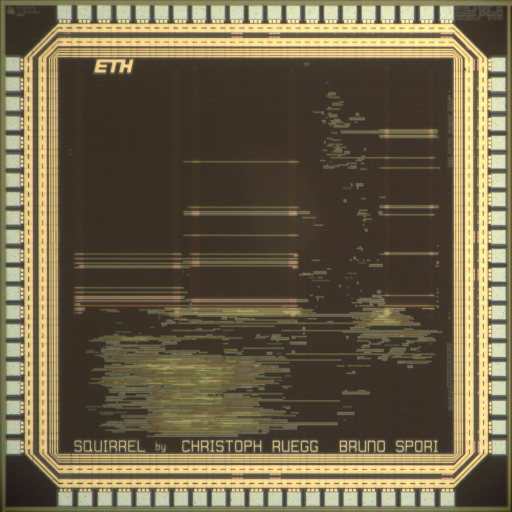

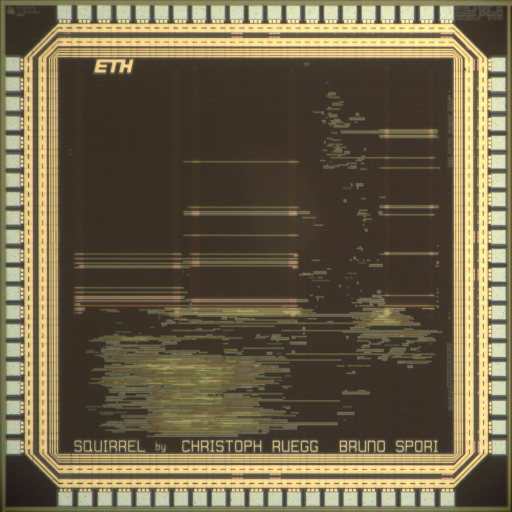

Squirrel (2006)

by

| Application | Processor |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 2.5 V |

| Clock | 125 MHz |

The Internet is constantly growing: the number of nodes is increasing and the achieved data rates become higher and higher. Today\u2019s large backbone networks use optical fibers as transport medium and can reach data rates of up to 10 Gb/s (OC192 lines). This means that the Internet nodes have to process data packets at the same high rate, which poses severe requirements to the employed hardware. The main bottleneck here is given by the memory access delay which limits the amount of memory accesses that can be performed per IP address lookup.

This semester thesis proposes a hardware implementation of a recently published IP address lookup algorithm for employment in backbone Internet routers. The concept of this algorithm is as follows: first, a specialized tree data structure is built by compressing IP address prefixes. Second, the tree is used to perform lookups in order to retrieve the information on which port to forward the incoming packets. Main advantages of this implementation are the low memory requirements to store a forwarding table and the few memory accesses necessary to perform a lookup.

The realized ASIC achieves a rate of 10 to 15 million lookups per second which is sufficient to support more than 1000 networks.