The IIS Chip Gallery

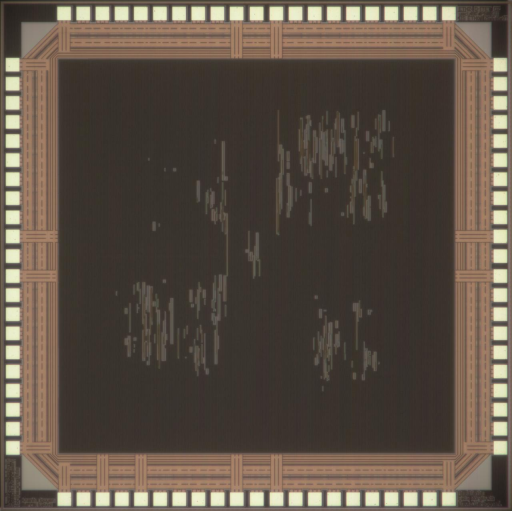

LSspeech (2007)

by

| Application | Low-power |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 1.8 V |

In this project, different clocking strategies have been compared in view of low power consumption. A typical speech-enhancement algorithm has been implemented and integrated in four variations on the same silicon die.

The first sub-design serves as reference with single-edge triggered one-phase clocking (SETOPC) and flip-flops from a standard cell library. The second design uses the same clocking strategy, but it contains redesigned flip-flops with reduced transistor widths. The third design features dual-edge-triggered one-phase clocking. Only half the SETOPC clock frequency is required in order to achieve the same throughput. Therefore, at least half of the power dissipated in the clock tree should theoretically be saved. The fourth design uses level-sensitive two-phase clocking and contains redesigned latches with reduced transistor widths. This clocking strategy allows the implementation of simpler, and therefore more power-efficient clock trees because of relaxed timing constraints.

All four designs have been verified on an ASIC tester. Unfortunately, no power savings could be observed in the second, third and fourth designs, compared to the SETOPC reference. A reason for this unexpected behavior might be the relatively small amount of sequential cells, compared to the high number of glitches inside the higher number of combinational cells.