The IIS Chip Gallery

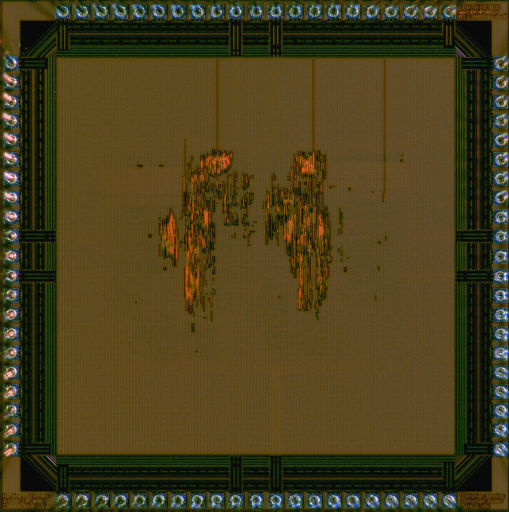

GKSVD (2007)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 40 kGE |

| Voltage | 1.8 V |

| Clock | 149 MHz |

Beamforming (BF) improves the error rate performance of multiple-input multiple-output (MIMO) wireless communication systems. BF is achieved by multiplication of the transmit vector by a steering matrix, which is obtained through the singular value decomposition (SVD) of the channel matrix.

In this project, a hardware-efficiency optimized VLSI architecture for steering matrix computation has been developed. To this end, the well-known SVD algorithm of Golub et al. has been optimized for VLSI implementation. A high-speed Givens rotation unit has been employed, which uses CORDIC arithmetic and complex-valued multipliers in order to achieve a high processing throughput at low silicon area. The arithmetic precision has been optimized to achieve sufficient precision for MIMO communication systems.

The steering matrix computation architecture has been implemented in 0.18 mm CMOS technology and uses 42.3 k gate equivalents at 149 MHz and requires only 3.3 ms per 4x4-dimensional steering matrix computation. A comparison with the SVD implementation of Studer et al., 2007, has shown a three-fold hardware-efficiency gain of the optimized steering matrix computation unit.