The IIS Chip Gallery

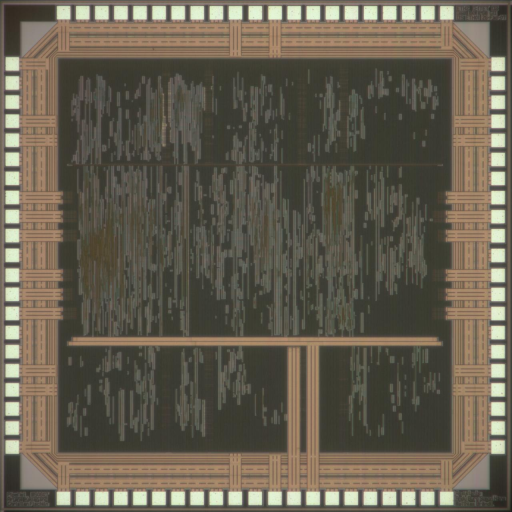

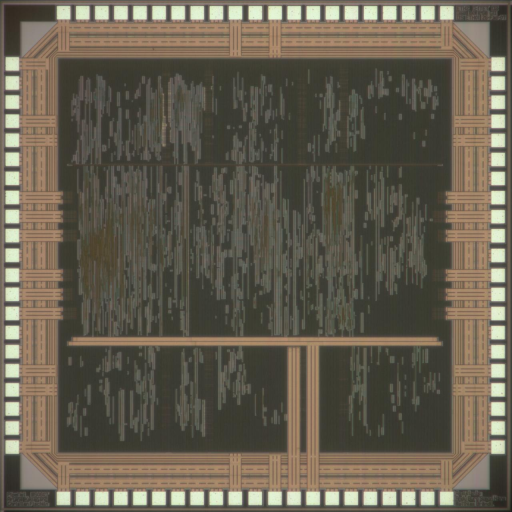

PipeNet (2007)

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm 3GE |

| Voltage | 1.8 V |

| Clock | 280 MHz |

Systems on Chip (SoC) in deep-submicron technologies are comprised of many Virtual Components (VC, also IP). Traditionally, these VCs are connected through shared busses or crossbar switches. However, as technology proceeds to the 45 nm node, routing delay becomes one of the performance-limiting factors and conventional interconnect structures can no longer handle the rapidly increasing need for higher communication bandwidth.

Networks on Chip (NoC) are a promising new approach to alleviate this communication bottleneck between SoC building blocks. Similar to computer networks, such onchip networks are comprised of network interfaces and switches that can be arranged in different topologies to meet the bandwidth and latency requirements of the system. XPipes is such an NoC architecture.

The goal of this project was to study and optimize the register- transfer-level implementation of the XPipes building blocks and to demonstrate the technology. To this end, a XPipes network with 6 traffic generators and 6 memories has been implemented in a 0.18 mm technology. The design uses area-optimized latch-based FIFOs for the network switches and has a separate power supply for the NoC components. The fabricated ASIC operates at maximum clock frequency of 280 MHz, while 340 MHz operation was expected from post-layout static timing analysis.