The IIS Chip Gallery

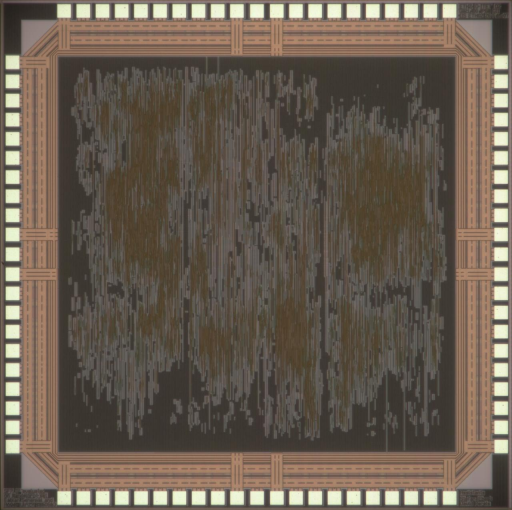

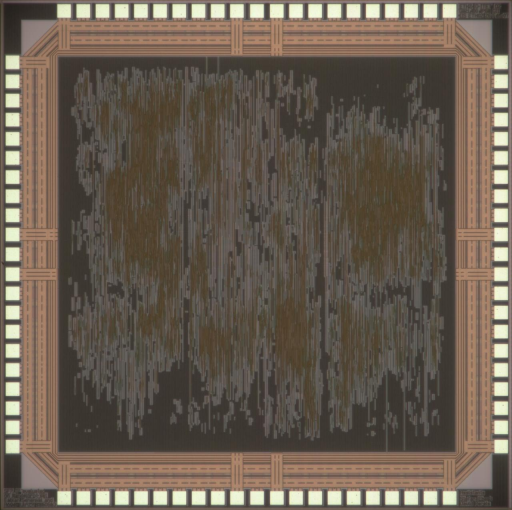

SFP (2007)

by

| Application | Fun |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 1.8 V |

| Clock | 100 MHz |

One of the major issues of industrial IC design is the duration of the design cycle. Depending on the project complexity, eight to twelve months may elapse from project start until tape out. A reduction of this time span results in a major economical benefit. Extensive re-use of design parts from previous projects, integration of virtual components (also known as IPs), and application of scripts for task automation are common practice to reach this goal.

The topic of this semester thesis was the implementation of a virtual component providing a shared function pool (SFP) of a set of user-defined mathematical operations (e.g. division, multiplication, CORDIC, etc.). This pool can be accessed (shared) by any number of different client circuits. In this way, the design efficiency can be enhanced by reducing the silicon area.

In addition, the modular and library-based implementation as virtual component enables rapid instantiation and customization in different projects of the SFP, shortening the over all design time.

As a proof of concept an SFP-supported processor has been implemented in silicon, which has been programmed to compute Mandelbrot sets for demonstration purposes. On average 4.4 million pixels per second can be processed.