The IIS Chip Gallery

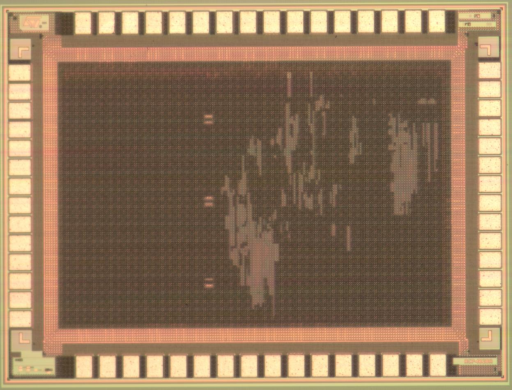

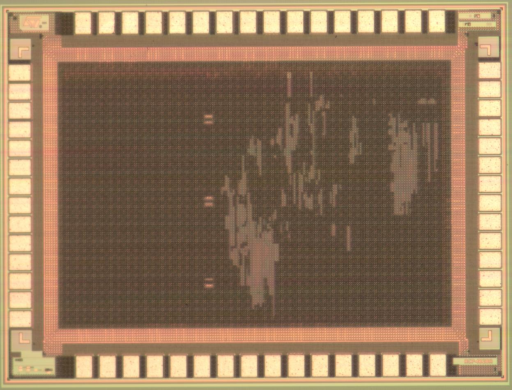

V2Turbo (2007)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | STM |

| Type | Research Project |

| Package | QFN64 |

| Dimensions | 1353μm x 885μm |

| Gates | 40 kGE |

| Voltage | 1.2 V |

| Power | 61.5 mW (176MHz) |

| Clock | 246 MHz |

The high power level of 3G mobile phones, especially at the high data rates supported by High Speed Downlink Packet Access (HSDPA), still impedes the migration of users to the next generation of mobile phones. Therefore, new low-power, low-cost solutions for HSDPA signal processing blocks are required to guarantee the future sucess of 3G mobile phones.

Turbo decoders are specified for the baseband part of the receiver in HSDPA mobile phones. In this project, several turbo decoder structures have been investigated, simulated and compared. Various architectural trade-offs have been analyzed and appropriate choices have been made to achieve the high data rates required by HSDPA at a low power level. Moreover, the turbo decoder has to handle all the specified block lengths to be standard compliant, which leads to a sophisticated design of the interleaver block.

An HSDPA compliant turbo decoder has been optimized at algorithmic, architectural and gate levels to overcome speed bottlenecks while being frugal in the use of silicon area and power.