The IIS Chip Gallery

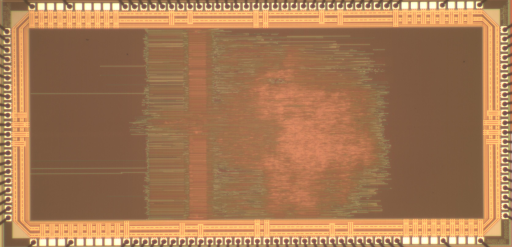

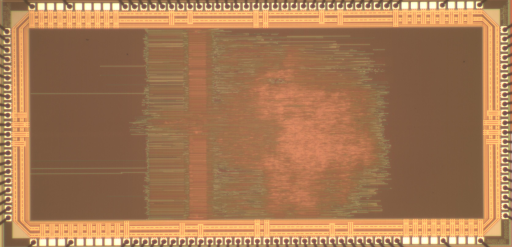

Frog (2008)

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | PGA120 |

| Dimensions | 5000μm x 2500μm |

| Voltage | 1.8 V |

| Clock | 208 MHz |

The quality-of-service and throughput requirements of modern wireless communication systems require high-performance error-correction schemes. Low-density parity check (LDPC) codes are promising candidates for next-generation wireless systems due to the excellent error-correction capabilities.

In this project, a configurable LDPC decoder architecture for quasi-cyclic (QC) codes has been designed. The proposed architecture is able to decode virtually any QC-LDPC code that fits into the allocated memories while achieving high decoding throughput. The VLSI implementation has been optimized for the IEEE 802.11n WLAN standard, but can be used for other standards as well. Additionally, low-power techniques (e.g., clock gating) have been employed in order to reduce the power consumption of the decoder.

The QC-LDPC decoder has been implemented in 180 nm CMOS technology, requires a core area of 3.39 mm2, and achieves up to 780 Mbit/s decoding throughout at a maximum clock frequency of 208 MHz. The energy efficiency is ranging from 1.9 nJ/bit to 6.0 nJ/bit, depending on the block-length and the code rate. Comparisons with non-configurable LDPC decoders have shown that the flexibility of this architecture does not lead to a performance penalty, neither in terms of area, throughput, or energy-efficiency.