The IIS Chip Gallery

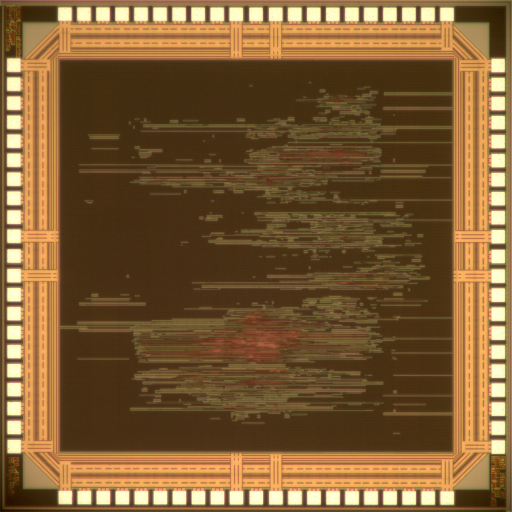

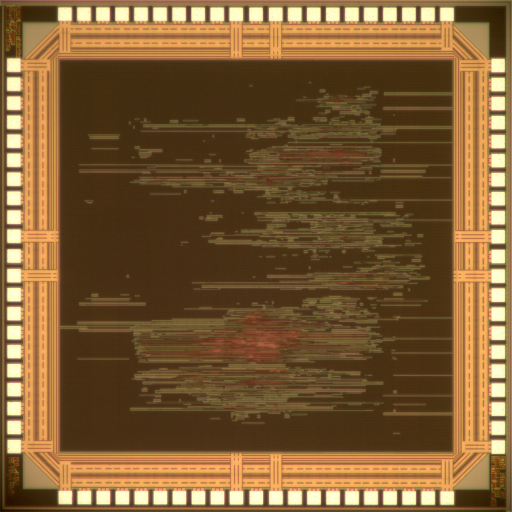

Gram_Schmidt (2008)

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 1.8 V |

| Clock | 162 MHz |

The QR decomposition (QRD) is an important matrix decomposition method for many detection algorithms in multiple-input multiple-output (MIMO) systems. It is, for example, used as preprocessing for ordered successive interference cancellation (OSIC) and tree-search-based detection schemes. There exist different algorithms for the implementation of QRD, for instance Givens rotations, Gram-Schmidt, or Householder reflections. This work focuses on the VLSI implementation of an iteratively sorted Gram-Schmidt (GS) algorithm.

Although it is well known that the numerical stability of the GS-based QRD is critical, the numerical properties have shown to be adequate for a dedicated VLSI implementation after a thorough investigation and the development and application of a reduced floating-point technique.

The GS algorithm has been implemented as VLSI architecture for MIMO preprocessing employing minimum mean squared error (MMSE) sorted QR decomposition (SQRD). Two versions of the architecture were successfully integrated as ASIC in UMC 180 nm 1P/6M CMOS technology.