The IIS Chip Gallery

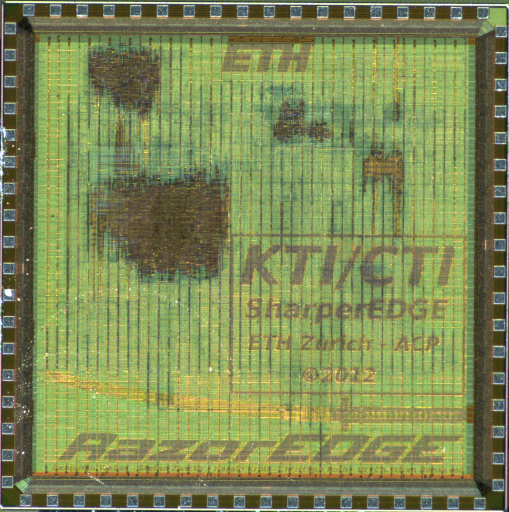

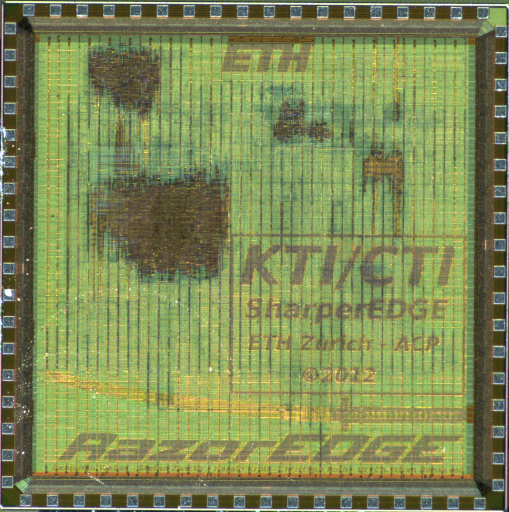

RazorEDGE (2012)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | SMIC |

| Type | Research |

| Package | QFN56 |

| Dimensions | 3000μm x 3000μm |

| Gates | 800 kGE |

| Voltage | 1.2 V |

| Power | 56 mW (1.2V, 100MHz) |

| Clock | 104 MHz |

This chip performs evolved edge baseband signal processing. It includes, digital front-end, equalization and channel decoding. In addition the entire physical layer control functionality is included. As an added feature, the chip has incremental redundancy including its control unit. This chip was done as part of the CTI/KTI project SharperEDGE, this explains also the name of the chip, which means the chip sharp as a razor, for the logo, we went a step further and added a katana for good measure.

The ASIC comprises transmitter and receiver with detector and a decoder with an autonomous incremental redundancy implementation. The ASIC reaches a measured sensitivity of -111.8dBm for single antenna GSM voice channels and achieves the reference interference performance for adjacent channels 12 dB above 3GPP requirements. It occupies 6mm2 in 130nm CMOS with a power consumption between 5 and 39mW.