The IIS Chip Gallery

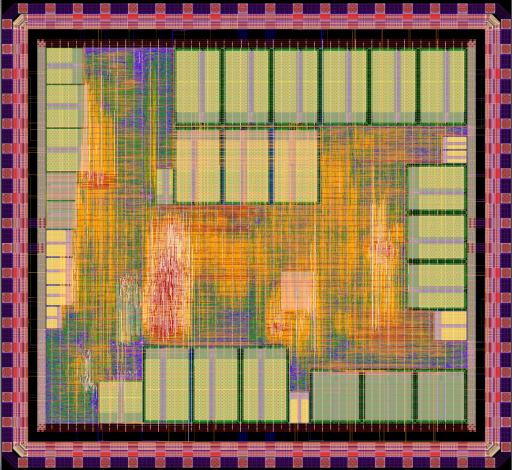

Invictus (2014)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | SMIC |

| Type | Research |

| Package | QFN56 |

| Dimensions | 3432.09μm x 3131.97μm |

| Gates | 600 kGE |

| Voltage | 1.2 V |

| Power | 30 mW (@128MHz, 1.2V) |

| Clock | 180 MHz |

The Invictus ASIC is a digital baseband downlink receiver for the enhanced 3G standard TD-HSPA+ LCR. It supports all modulation schemes (QPSK, 8PSK, 16QAM, 64QAM) and all channel coding schemes (convolutional and turbo) including the hybrid-ARQ feature of the standard. The ASIC receives digital I/Q samples at the input and provides the decoded transport block bits at the output.

Invictus contains roughly 550kGE of logic and 650kBits of on-chip SRAM. Invictus B1 is a redesign of this chip.