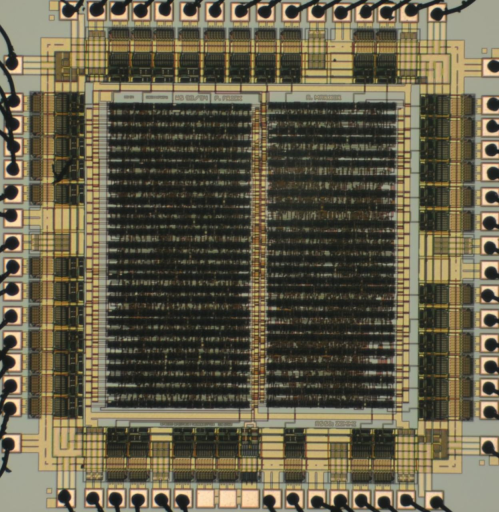

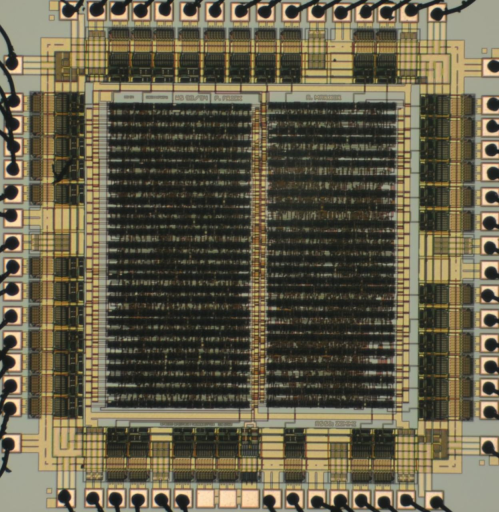

The IIS Chip Gallery

SST (1993)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Semester Thesis |

| Package | PGA84 |

| Dimensions | 3200μm x 3200μm |

| Gates | 5 kGE |

| Voltage | 5 V |

| Clock | 180 MHz |

A spread-spectrum transmitter ASIC (SST) has been devloped as a student project. All digital parts of the transmitter of a direct-sequence spread-spectrum modem are incorporated on one chip. This includes BPSK/QPSK data modulation and differential encoding, BPSK/QPSK spreading by a pseudo noise (PN_ code sequence, and pulse shaping through a matched filter and intermediate frequency modulation. Two configurable PN code generators for code lengths of 15-1023 as well as a three-wire bus interface for control purposes are also integrated on to the ASIC. The desired output sample rate of 100 MHz is achieved through an elaborate circuit architecture using pipelining and replication.

A maximum clock frequency of 110 MHZ is guranteed, which allows data rates of up to 3.6 Mbits/s. On tests on an HP83000 ASIC tester, functionality was observed at a frequency of up to 180 MHz. Central clock buffering and special layout partitioning has been used in order to achieve the highest possible speed.