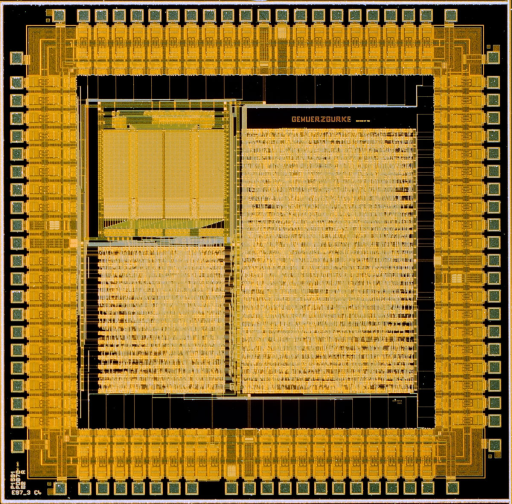

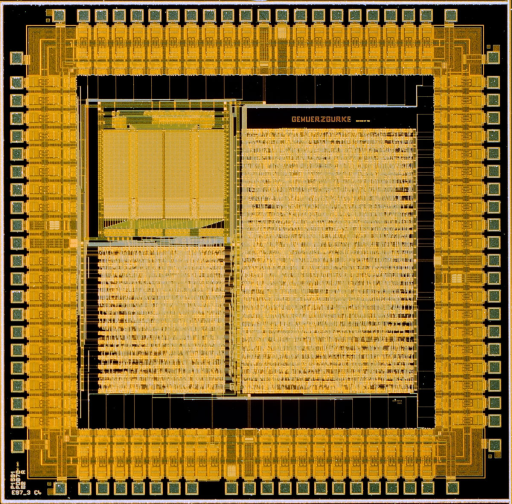

The IIS Chip Gallery

Gewuerzgurke (1996)

by

| Application | Industrial |

| Technology | 800 |

| Manufacturer | ES2 |

| Type | Semester Thesis |

| Package | PGA84 |

| Voltage | 5 V |

The bandwidth of serial and parallel computer interfaces is often too low for many applications. Most of todays computers/workstations provide a SCSI interface which allows to connect different devices with transfer rates up to 10 Mbytes per second or even more. Examples of such devices are digital audio interfaces, ISDN modems or personal video systems.

The aim of this semester thesis was to develop a SCSI interface ASIC implementing several data channels equipped with FIFOs.

The ASIC contains a SCSI port, a microprocessor core, a FIFO controller which manages an external DRAM, and a generic interface. The microprocessor handles the SCSI Protocol. To support the different SCSI standards the instructions are stored off-chip in an EPROM and are cached on-chip. The FIFO controller organizes the external DRAM in up to 256 different channels and generates DRAM addresses and control signals. The generic interface supports a four-phase handshake protocol. It is bidirectional and has a data channel selector.