The IIS Chip Gallery

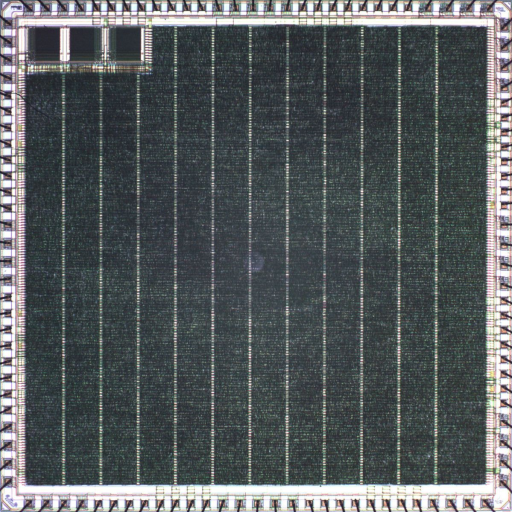

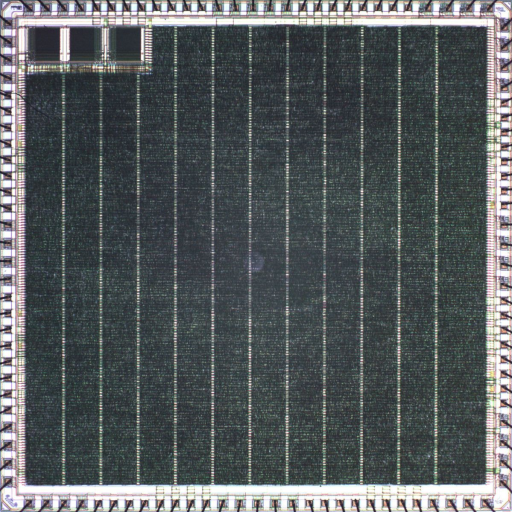

Adante (2000)

by

| Application | Communication |

| Technology | 350 |

| Manufacturer | austriamicrosystems |

| Type | Research |

| Package | LCC100 |

| Dimensions | 8185μm x 8185μm |

| Gates | 200 kGE |

| Voltage | 5 V |

| Power | 1000 mW |

| Clock | 47 MHz |

The objective of the European project ADAMO was to validate the potential of small, low-cost adaptive antennas for HIPERLAN I (= ESTI standard for wireless LANs) modems. Improvement of performance and reduction of power consumption are the expected benefits of adaptability.

Instead of using a complex, high-speed (47 Msamples/ s) adaptive equalizer (= digital transversal filter) to mitigate the detrimental effects of intersymbol interference caused by multipath propagation, spatial filtering is applied by appropriately weighting and combining the RF signals from three independent antennas.

This beam-forming network realized with analog phase shifters and amplifiers consumes considerably reduced power compared to a digital equalizerbased solution.

IIS' contribution was the implementation of the digital signal processing algorithm for the computation of the combiner coefficients of the adaptive antenna. A dedicated ASIC - the AdAnTE chip - has been designed. This high-speed digital chip with 780,000 transistors calculates the set of coefficients on a linear systolic array of pipelined CORDIC (COordinate Rotation DIgital Computer) processor elements in less than one microsecond.

IP Core for Real-Time Solution of Least-Squares Problems using CORDIC and QRD-RLS

The famous least-squares method was introduced by Gauss in 1795 for the use in survey evaluation and astronomical calculations. Nowadays image processing, robotics or communications are requiring realtime solutions of least-squares problems.

This project arose from the development of a wireless LAN receiver using an adaptive antenna array. The amplitudes and phases of the antenna mixer are determined by comparing received training sequences to the expected undisturbed data. By far the most expensive part of the processing is the least-squares calculation. The combination of QR (triangular) decomposition and recursive least-squares computation is known as the QRD-RLS algorithm (QR-Decomposition Recursive-Least-Square). It is robust, effective, and an implementation using CORDIC processors maps very well to VLSI.

The developed processor array is reusable as an IP core since it is largely scalable. A graphical user interface simplifies to handle all parameters: Transformations from fully parallel to fully sequential processing through several circuit levels can be selected. This enables customizations that closely meet the requested throughput with minimal area consumption. A preview shows the resulting architecture as well as the arrays overall area. Finally, the array is exported as Matlab and VHDL source.