The IIS Chip Gallery

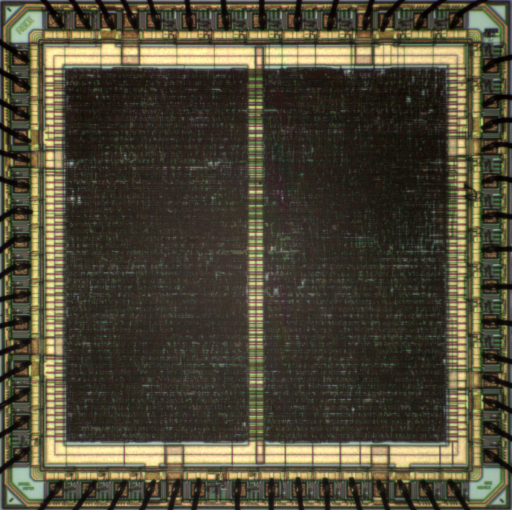

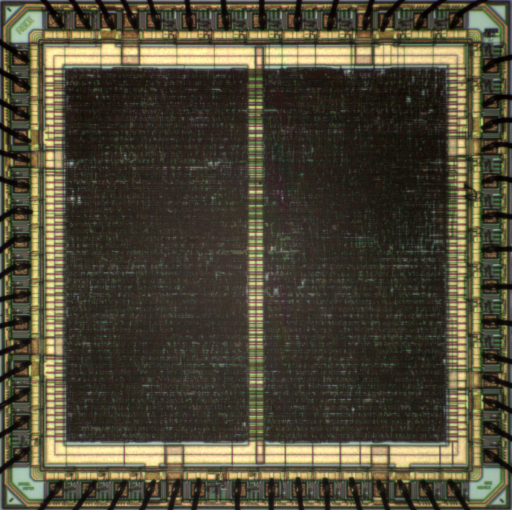

ASDI (2000)

by

| Application | Converter |

| Technology | 600 |

| Manufacturer | austriamicrosystems |

| Type | Semester Thesis |

| Package | LCC68 |

| Dimensions | 3400μm x 3400μm |

| Voltage | 3.3 V |

In this semester project, a configurable digital decimation filter and uC interface for use with existing (commercial) isolated Sigma Delta modulators has been developed. These isolated A/D converters provide the current measurement for power supply applications. One specialty of this application is the use of a Sigma Delta converter in a control loop, which leads to constraints on the group delay of the decimation filter. Furthermore, the filter has to be configurable for operation at different points of the resolution vs. conversion rate curve.

The implemented chip can be connected to four isolated modulators, each running at its own clock rate (since the modulators cannot be clocked externally). Internally, the different clock domains are decoupled using asynchronous FIFO\u2019s. The samples are filtered and decimated according to the configuration set via the uC interface. The final samples can again be read out via the same interface. The nominal sample rate and resolution points are 20 kS/s at 9.5 bit, 10 kS/s at 12 bit and 5 kS/s at 13.5 bit effective resolution. Optionally, the chip can align the sampling points to a configurable phase with respect to a periodic trigger command on the uC interface. The circuit has been tested successfully on an IC tester, though not yet in the real application environment.