The IIS Chip Gallery

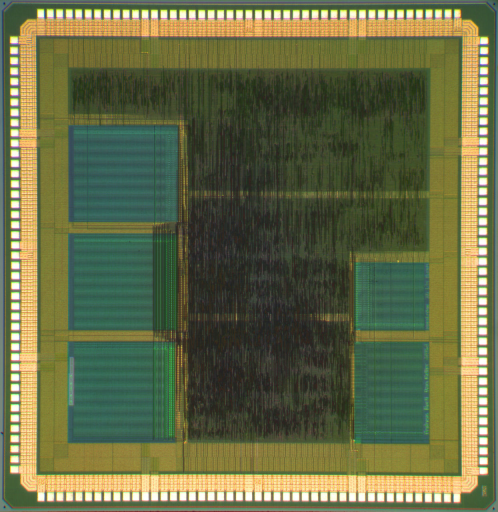

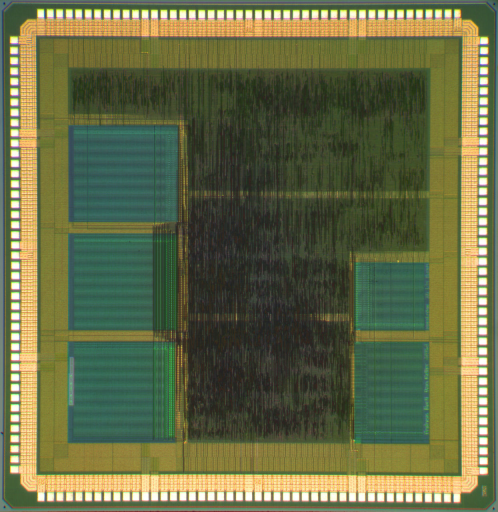

3D_DCT (2000)

by

| Application | Graphics |

| Technology | 350 |

| Manufacturer | Mietec |

| Type | Diploma Thesis |

| Package | PGA208 |

| Dimensions | 5250μm x 5250μm |

| Gates | 500 kGE |

| Voltage | 3.3 V |

| Clock | 100 MHz |

Traditional video compression algorithms are based on motion estimation techniques. The three-dimensional discrete cosine transform (3D-DCT) approach offers the advantage of reduced computational complexity, independent of the target compression ratio. This, together with the symmetrical properties of encoder and decoder, facilitates a very efficient hardware implementation.

In this diploma project, the first VLSI implementation of the 3D-DCT algorithm for a complete single-chip video compression/decompression system has been established. A detailed trade-off analysis for subtasks such as 3D-DCT computation, quantization, zero-runlength and variable-length encoding has been performed in terms of computational complexity, compression ratio, peak signal-to-noise ratio, as well as chip area and power consumption. As a result, the 3D-DCT has been implemented by one 1D-DCT unit with a single processor core per color channel. For variable-length coding a single-cycle Huffman coder has been chosen. Various pre-defined code books, optimized for different compression ratios, have been implemented.