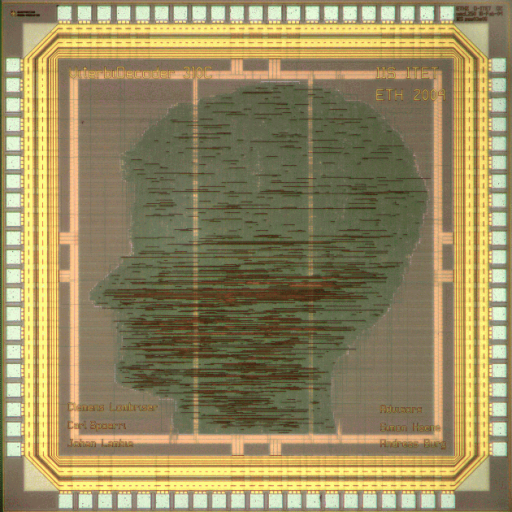

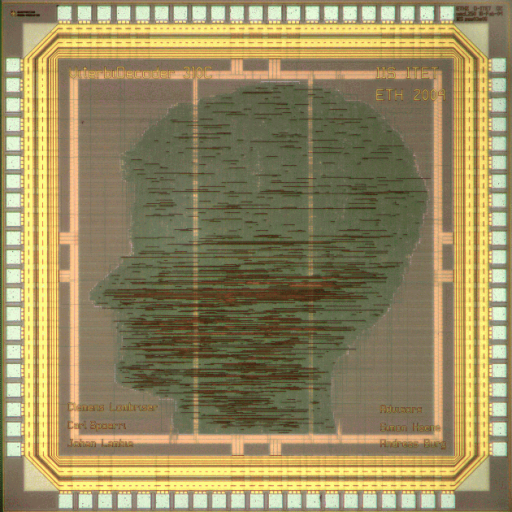

The IIS Chip Gallery

Viterbi (2004)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 90 kGE |

| Voltage | 2.5 V |

| Power | 475 mW, 2.5V, 100MHz |

| Clock | 225 MHz |

The viterbi decoder implemented by this chip is compliant to the error-checking code defined in the 802.11a wireless LAB standard which is a 64-state, rate 1/2 convolutional code. At each time step, the decoder computes a new poath metric for each of the 64 states, based on previously computed metrics. This computation is recursive and represents the performance bottleneck of hardware Viterbi decoders.

The extraordinary layout is obtained by modifying the standard cell rows individually during the floorplanning. Depicted is the head of one of the designers Clemens.