The IIS Chip Gallery

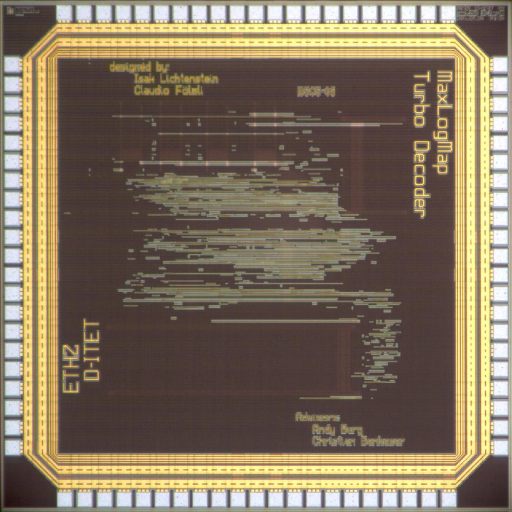

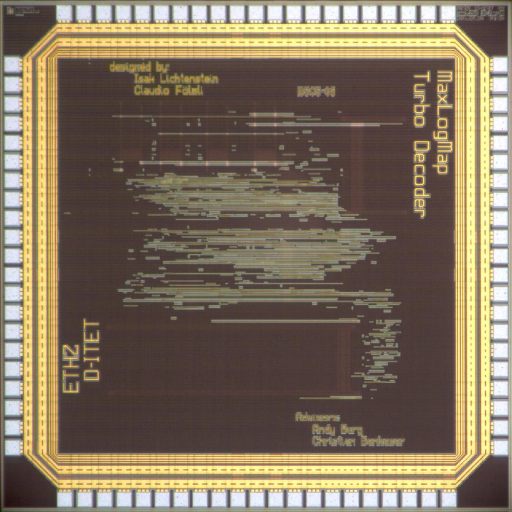

MaxLogMap (2006)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 2.5 V |

| Clock | 77 MHz |

Turbo codes were invented in 1993 by Berrou and have since then received significant attention due to their ability to perform close to the Shannon limit. In particular, turbo codes are included in the 3GPP standard where they are used for the encoding of high rate data traffic.

The goal of this project has been to implement an area-optimized turbo decoder ASIC according to the specification in the UMTS standard. To this end, the implemented circuit employs the BCJR algorithm with the sliding-window approach and makes use of the logMAP approximation. The corresponding architecture shares hardware resources for the forward and the backward iteration through the trellis graph and employs a dedicated unit for the LLR computation. On-chip memories hold the state metrics of the trellis and the extrinsic information that is passed from one turbo iteration to the next. Only the memories holding the a-posteriori outputs from the demodulator are kept off chip due to space limitations.

The design uses a core area of 2.26 mm2 in a 0.25 mm technology and achieves a throughput of 2.2Mbps with eight decoding iterations. This is sufficient for most data traffic applications in UMTS, while the emerging HSDPA standard requires higher throughput up to 14.4 Mbps.