The IIS Chip Gallery

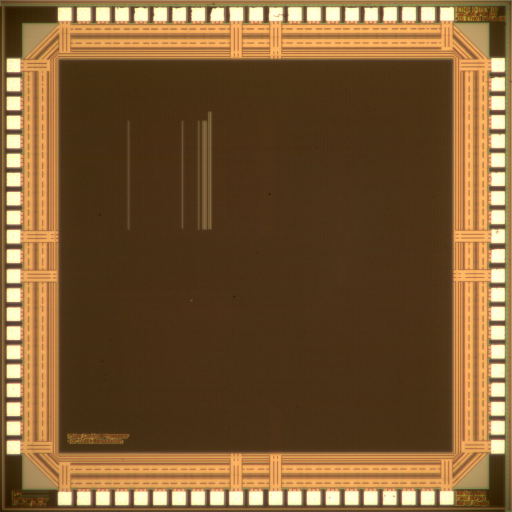

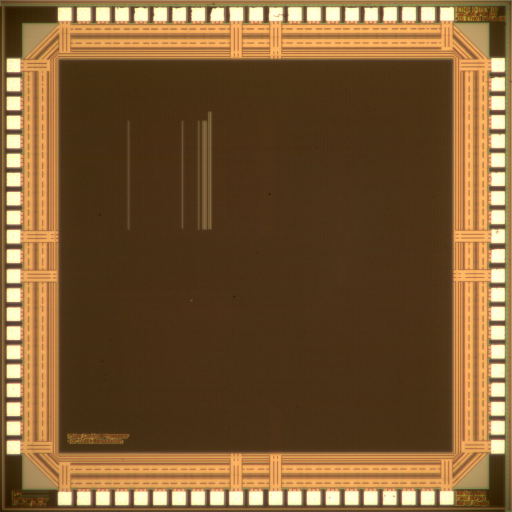

PCP (2008)

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 1.8 V |

| Clock | 300 MHz |

The Quantum Device Lab at the physics department of ETHZ investigates quantum properties of novel micro- and nano-structured electronic devices and their interaction with classical and quantum electromagnetic fields. To study and manipulate so-called quantum bits (Qubits), the generation of fast pulse sequences is necessary, which are currently generated by an arbitrary waveform generator (AWG). The goal of this project was to replace the AWG by a programmable pulse-control processor ASIC.

The pulse-control processor architecture contains an instruction memory, the pulse-control processor (PCP) itself, and a pulse-control arithmetic unit. The computation of the arbitrary waveforms is based on the method of finite differences and is carried out by the pulse-control arithmetic unit. The instruction set of the PCP developed during this thesis consists of 13 specific 16 bit instruction words that allow to generate any required waveform.

The realized ASIC contains two PCP cores and was designed to achieve a maximum clock frequency of 300 MHz. The silicon area occupied by the two cores is 0.74 mm2. The latency is three clock cycles. One core has 8 MByte instruction memory, while the other core is equipped with 4 MByte instruction memory. The ASIC was manufactured in UMC 180 nm CMOS technology.