The IIS Chip Gallery

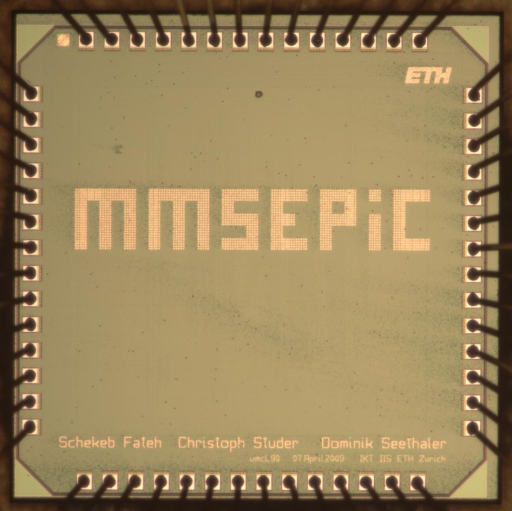

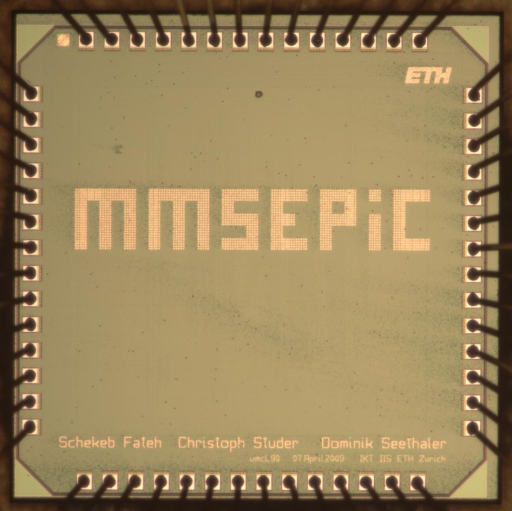

MMSEPIC (2009)

by

| Application | Communication |

| Technology | 90 |

| Manufacturer | UMC |

| Type | Diploma Thesis |

| Package | QFN56 |

| Dimensions | 1875μm x 1875μm |

| Gates | 400 kGE |

| Voltage | 1.2 V |

| Power | 768 mW |

| Clock | 568.18 MHz |

Iterative soft-input soft-output (SISO) detection and channel decoding is the key to achieve near-ideal capacity in multiple-input multiple-output (MIMO) wireless communication systems. In this project, we develop the first VLSI implementation reported in the literature of a 4-stream SISO detection algorithm for iterative MIMO decoding.

To this end, a reduced-complexity minimum mean-square error (MMSE) parallel interference cancellation (PIC) algorithm has been developed. The main complexity of the resulting algorithm is required by one matrix inversion per received vector. Efficient matrix inversion is achieved by performing an LU-decomposition followed by forwardand back-substitution procedures.

We developed a systolic network of dedicated processing units (PUs), which processes six receive vectors concurrently and in a pipelined manner. Each PU performs the assigned tasks in 18 cycles. Matrix inversion requires division operations, which are performed in custom units that meet the throughput and precision constraints.

The ASIC was fabricated in 90 nm CMOS technology. The implemented SISO MMSE PIC decoder, which covers 1.5 mm2 core area, performs 4-stream SISO detection with more than 8 dB SNR improvement over state-of-theart MIMO detector implementations, when performing four iterations. The detector achieves a maximum clock frequency of 568 MHz, leading to 757 Mb/s throughput per iteration. The corresponding power consumption is 768 mW.

The thesis of Christoph Studer, which also features this chip has won the ETH Medal for outstanding PhD thesis.

The design of this chip has won the 2010 Swisscom Innovation Award.