The IIS Chip Gallery

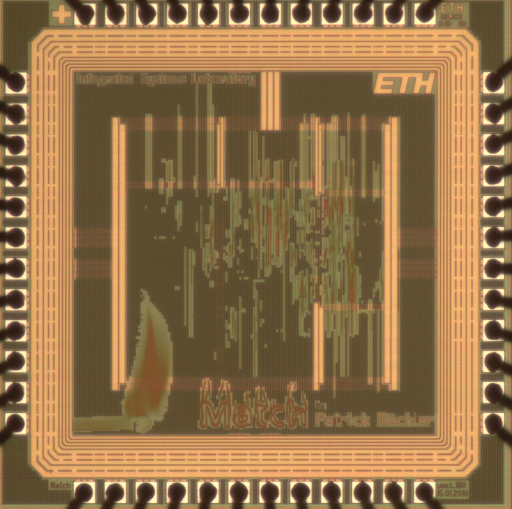

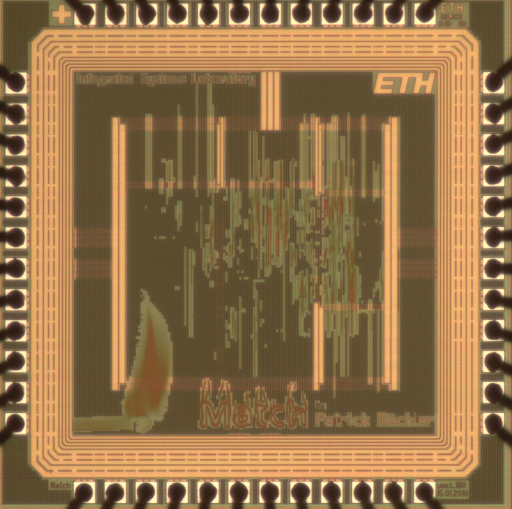

Match (2009)

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 40 kGE |

| Voltage | 1.8 V |

| Power | 88 mW |

| Clock | 135 MHz |

The emerging research field of compressed sensing (CS) promises better signal reconstruction out of fewer measurements if a sparse representation of the signal exists. Since wireless broadband channels often exhibit a sparse impulse response, CS reconstruction algorithms were proposed for channel estimation. In this paper, a hardware architecture for channel estimation using the matching pursuit algorithm is presented. The reference design targets the 3GPP LTE standard with a channel bandwidth of up to 20 MHz. Achievable performance gains over least squares channel estimation are illustrated by means of simulations. The costs in terms of chip area and reconstruction time for 180 nm CMOS technology are presented together with an analysis of the tradeoff between hardware complexity and reconstruction performance.